發佈日期:2024/8/1 SRAM 故障分析

發佈單位:iST宜特

SRAM 以其高速運作、低延遲和低耗能的特性,對於發展 AI 人工智慧所需的高效運算及機器學習至關重要。當IC內部的SRAM出現問題,雖然已知異常位置,但礙於SRAM結構密集且重複性高,如何得知更多異常點資訊,分析出異常真因是一大挑戰。

SRAM 故障分析

記憶體分為兩大類,第一類稱為「非揮發性記憶體」(non-Volatile),比如Flash(快閃記憶體),用於長期儲存資料;另一類則為「揮發性記憶體」(Volatile),包括DRAM(動態隨機存取記憶體,Dynamic Random Access Memory)和SRAM(靜態隨機存取記憶體,Static Random Access Memory),可即時高速運算暫存資料。兩者最大的差異,在於電源供應終止後,儲存的資料是否會消失。

SRAM和DRAM屬於揮發性記憶體,當晶片進行邏輯運算後,讀寫結果會暫存在SRAM和DRAM中,類似倉儲的角色。只要電源供應不中斷,SRAM和DRAM中的資訊就會一直存在。一旦電源關閉,SRAM和DRAM內儲存的資料將會消失。

相較於DRAM,SRAM具有靜態存取特性,不需要週期性地刷新數據,因此更加節能,耗電量也更少。此外,SRAM透過開關電晶體即可讀取數據,存取時間較DRAM快速,這使得SRAM成為應用於CPU和GPU中快取記憶體的主流選擇。

台積電在2022年IEDM (International Electron Devices Meeting )會議中表示,其三奈米(N3)製程的 SRAM 面積僅比五奈米(N5)製程縮小約5%,同時,Intel 4製程的SRAM密度相較於Intel 7製程也僅微縮了約23%。儘管大廠在不斷精進的先進製程中面臨SRAM微縮挑戰,SRAM技術在AI人工智慧和高效能運算(HPC)晶片等先進應用中的重要性依然不減。

為滿足高階晶片在效能與功耗上的更高需求,晶片設計研發團隊正不斷尋求提升CPU性能的解決方案,SRAM晶片的堆疊設計便是其中之一。許多設計在CPU上方堆疊SRAM晶片,以達到 PPA(Power/功率、Performance/性能、Area/面積)的多重需求。但當IC中存在許多結構相同且密集的SRAM,一旦IC SRAM發生故障,如何進行故障分析,增強晶片的良率和穩定性非常重要。因此,本期宜特小學堂將從SRAM操作原理談起,進而介紹常見的失效模式,再透過宜特故障分析實驗室專業團隊提供的分析協助您找出異常點真因。

SRAM 故障分析

SRAM 故障分析

一、SRAM的讀寫原理

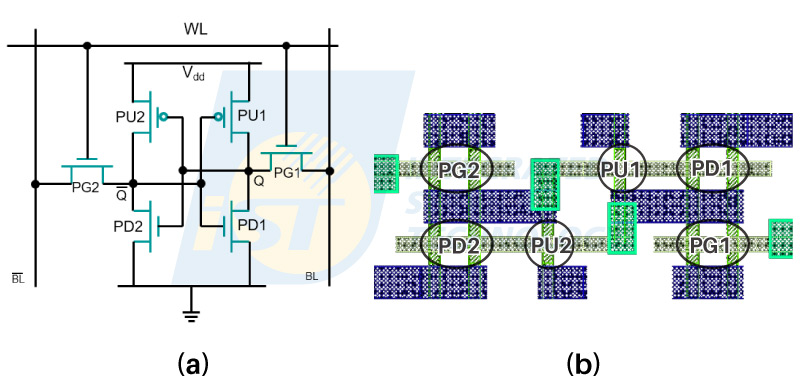

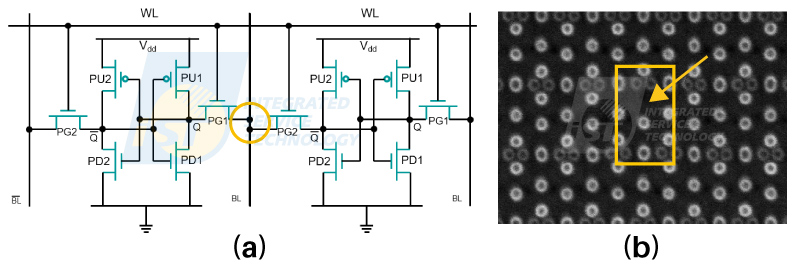

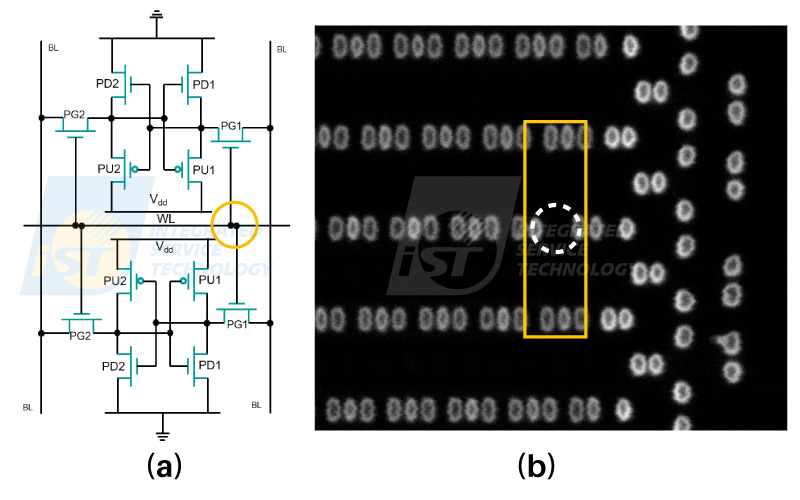

SRAM單一位元(bit)可由六個(6T)、八個(8T)、十個(10T)電晶體所組成,每個位元甚至也有使用更多電晶體的設計以實現多埠(Port)的讀寫功能,其中,以6T SRAM架構最為常見。6T SRAM由六個電晶體組成(圖一),分為2個PMOS的Pull Up(PU),4個NMOS的Pull Down(PD)及Pass Gate(PG),這裡PU和PD形成一個反相器,兩對PU與PD構成的兩個反相器利用線路形構成互鎖結構,實現資料的保存。PU也稱為Load Transistor,負責實現節點的高電位,即1的狀態,PD也稱為Drive Transistor,負責實現節點的低電位,即0的狀態;在一個bit中,透過兩個節點(Q和Q)高低電位互換,就能實現0和1兩種狀態的存儲,PG也稱為Access Transistor,負責實現位元線(Bit Line, BL)的訊號接入,以實現讀寫功能。

6T-SRAM做讀寫動作時都需打開字線(Word Line,WL),如果要將資料寫入,則要將位元線(BL)及BL固定在一組固定的電壓,強制 bit-cell內儲存資料的節點 Q 及Q轉換狀態。當欲寫入1時,BL電壓為元件中的工作電壓(Supply Voltage for the Drain,VDD),BL電壓為0;而想寫入0時,BL電壓為0,BL電壓為 VDD。寫入動作是利用外部電壓源強行改變bit-cell (Q,Q)的內容 (由外部影響內部)。

至於讀取資料時,一樣要將WL打開,即將 WL 拉到 VDD。和寫入動作不同的只是BL和BL的狀態。讀取前,需將BL和BL的電壓拉到相同的電位,也就是 V(BL)=V(BL),稱為 pre-charge voltage,一般多為 VDD 或 (VDD – VT)。讀取的動作是將外部BL及BL平衡(pre-charge),然後讓bit-cell(Q, Q)的內容去影響BL和BL(由內部影響外部)。由於bit-cell的驅動力很小,需要仰賴感測放大器(sense amplifier)來放大BL及BL的差異,以讀取出0或1。

二、常見的SRAM失效模式

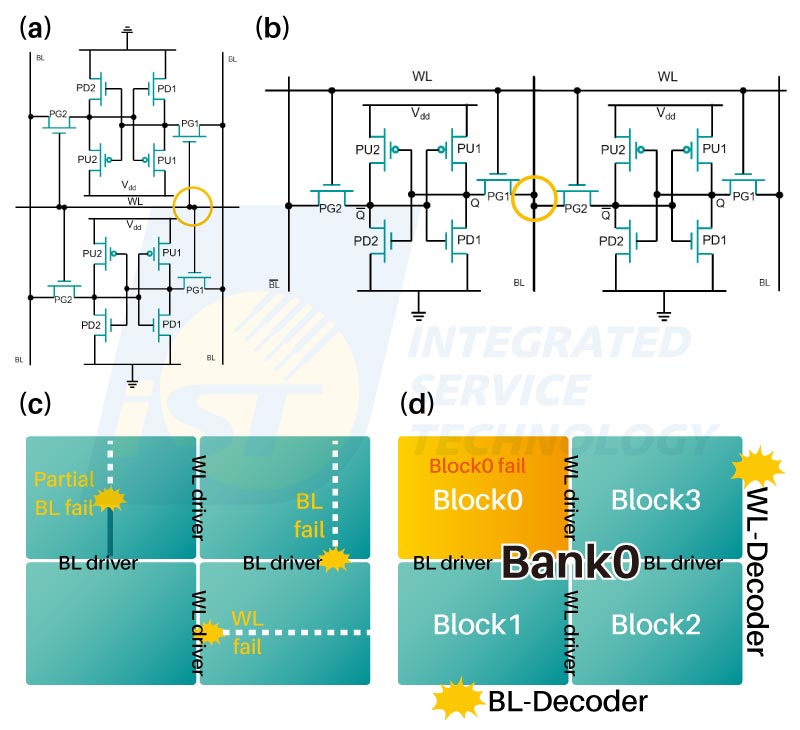

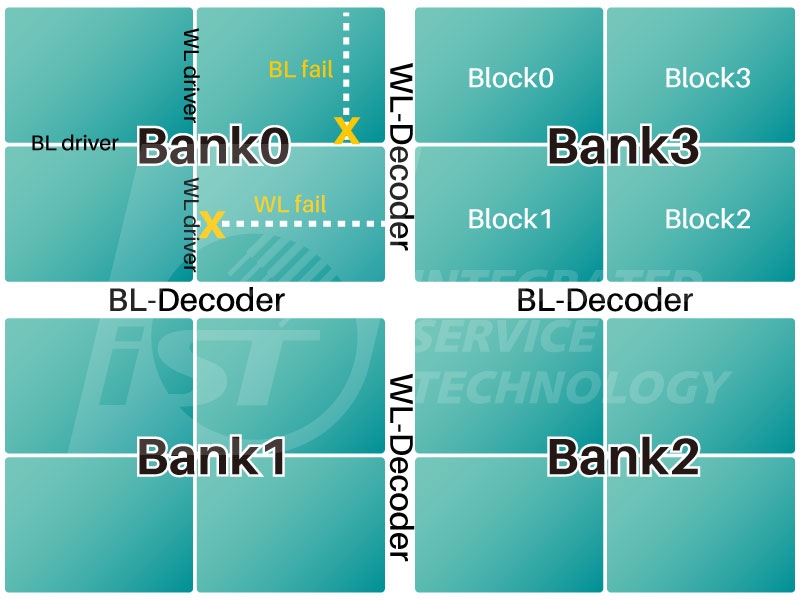

根據上一節SRAM操作原理介紹,我們可以SRAM異常點出現的位置,將SRAM的失效模式分成以下多種常見的失效模式:單位元失效(Single bit failure)、雙位元失效(Twin bit failure)、四位元失效(Quad bit failure)、部分位元線失效(Partial bit line)、位元線失效(Bit line failure)、字線失效(Word line failure)、區塊失效(Block failure)等(圖二)。在進行故障分析之前,宜特科技建議,如果能先確認失效位元的失效模式,將可加速後續的分析進展。

(一)單位元失效(Single bit failure):

單位元失效又可細分為恆態單位元失效 (hard single bit)與暫態單位元失效 (soft single bit)兩種失效模式。恆態單位元失效,是指該位元在不同電壓下都無法正常運作;暫態單位元失效 (soft single bit)失效,則指該位元僅在特定電壓下無法正常運作。

如一開始介紹,PU、PD或PG是構成SRAM的基本元件,Hard single bit的異常真因會落在PU、PD或PG的元件異常運作,或是連接這些元件的線路上。而Soft single bit的失效成因,則以PU、PD或PG元件微漏電或高阻值異常,甚或是各對PU、PD或PG之間電壓值差異所導致。

(二)雙位元失效與四位元失效(Twin and Quad bit failure):

當發生雙位元或四位元失效時,因其為相鄰位元遭受功能失效異常,我們可以專注在失效位元共用的線路上進行分析檢測,常見的異常通常是其共用線路上金屬層串接異常所導致。

(三)部分位元線失效(Partial bit line):

此失效模式是指該位元線上,部分位元操作正常,但其他使用同一條位元線上的位元無法正常運作,這部分常見的失效真因是位元線在正常與異常位元轉換交界處發生線路異常。

(四)位元線失效(Bit line failure):

此故障模式與部分位元線失效類似,但其發生異常的真因位置是落在SRAM 陣列旁的位元線控制電路,而非在SRAM陣列之內。

(五)字線失效(Word line failure):

此故障模式與位元線失效類似,只是發生在字線上,但往往發生異常的真因位置是落在SRAM 陣列旁的字線控制電路。

(六)區塊失效(Block failure):

此故障模式與位元線或字線失效類似,但因其異常是整個區塊失效,異常真因位置是落在SRAM 陣列旁控制該區塊的控制電路之上。

三、常見的SRAM失效模式故障分析手法

接著,宜特專業團隊將針對上述列出的SRAM失效模式一一介紹各自的故障分析手法。

(一)單位元失效分析方式:

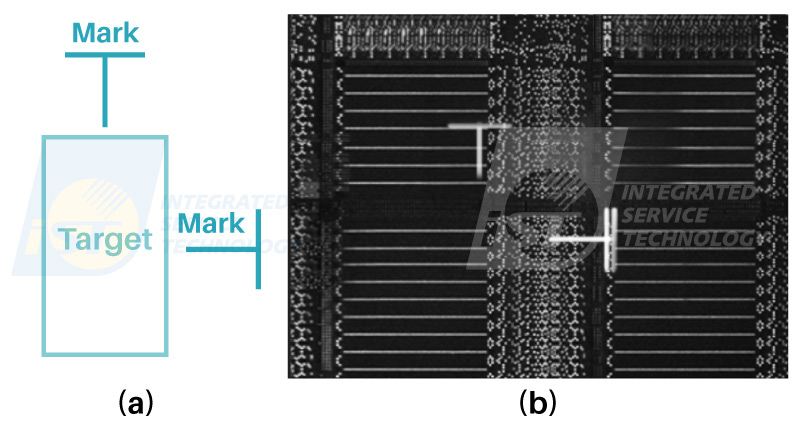

當遇到此類異常時,宜特科技故障分析實驗室會先將試片去層至相關電路層次(如Metal3)進行FIB (Focused Ion Beam, 聚焦離子束) 失效位元標示作業(圖三),以便後續失效位元定位更加精準。接著,我們會利用掃描式電子顯微鏡 (SEM)和導電式原子力顯微鏡 (C-AFM)從影響該SRAM電路架構的最上層電路層次開始逐層搜索。若後段製程中的金屬層被排除異常,我們可以再利用奈米探針電性量測( Nano Prober)針對PU、PD或PG的元件特性進行電性量測,根據SEM與電性量測結果進一步評估後,可以考慮進行後續的FIB或穿透式電子顯微鏡 (TEM) 分析,以呈現相關物性異常,以利後續的真因改善作業。

(二)雙位元失效與四位元失效分析方式:

當遇到此類異常時,我們會先將試片去層至相關電路層次(如Metal 5)進行FIB標示作業,好讓後續失效位元定位更加精準。接著,我們會利用SEM和C-AFM從該SRAM電路架構的最上層電路層次開始逐層搜索。我們可以利用SEM和C-AFM分析手法針對失效位元共用的線路進行分析檢測,並搭配後續的FIB或TEM分析將真因呈現。

(三)部分位元線失效分析方式:

在去層分析之前,此失效模式可先利用雷射光束電阻異常偵測 (OBIRCH) 和砷化鎵銦微光顯微鏡 (InGaAs) 進行亮點定位,以再確認物性異常位置; 其後,再依上述去層、FIB定位與分析手法進行真因追蹤。

(四)位元線失效/ 字線失效/ 區塊失效分析方式:

這些失效模式都與SRAM周邊控制電路(Peripheral circuit)相關。此類異常可先利用OBIRCH和InGaAs進行亮點定位縮小異常搜尋範圍,再依定位亮點位置進行去層,並搭配SEM、C-AFM和Nano Prober分析手法進行異常點確認,再以後續的FIB或TEM分析呈現真因。

四、SRAM故障分析案例分享

(一)恆態單位元失效(hard single bit)故障分析案例 :

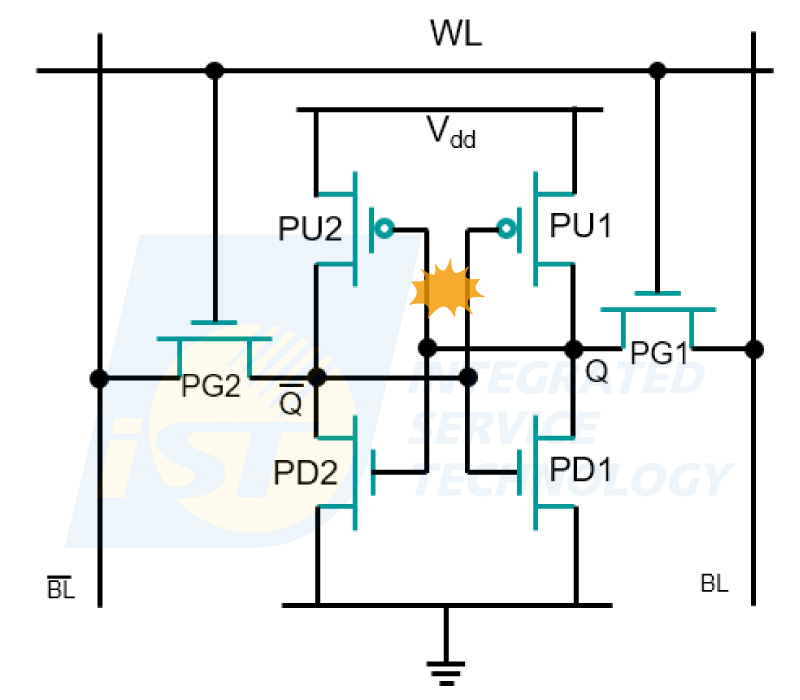

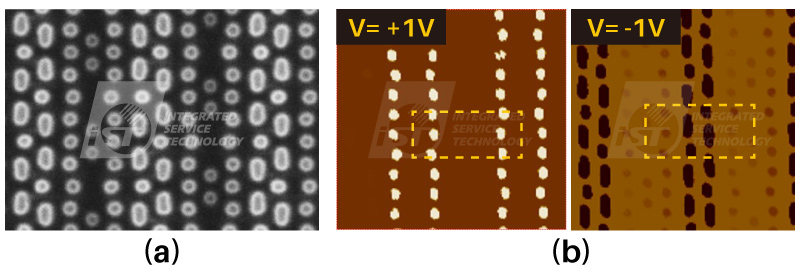

在這個恆態單位元失效的例子中,將PD1與PU1串接起來的結構(Butted contact)和將PD2與PU2串接起來的結構有互相短路的現象(圖四),因為這兩個串接結構屬同樣電氣性質,於SEM VC與C-AFM皆無法觀測到其異常(圖五(a)(b))。在這個案例中,我們使用Nano Prober進行兩個結構對點,便可發現此兩個原不應相連的電路結構有互相短路的現象(圖六)。

(二)暫態單位元失效(Soft single bit)故障分析案例 :

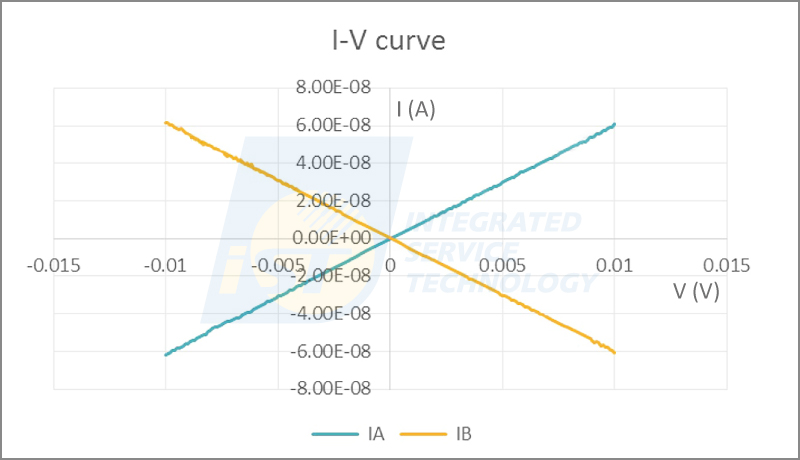

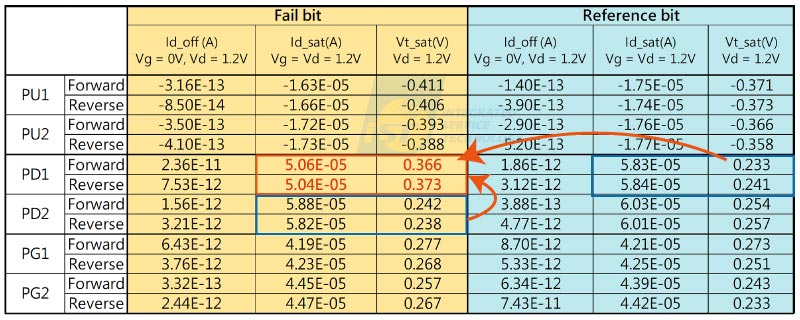

在暫態單位元失效這個案例中,SRAM單元內的兩組反向器因開關電壓不一致,導致暫態單位元失效。這種情況下,我們無法透過SEM VC進行異常偵測。此時,我們使用Nano Prober對SRAM內的六個電晶體元件進行各自的電性量測。結果顯示,失效位元在其PD1的閾值電壓較正常電晶體偏大超過100mV。經過電路設計者將該量測數據回饋到電路模擬後,驗證了該閾值電壓的明顯差異確實可造成此暫態單位元失效異常(圖七)。

在解析一個產品SRAM的故障分析中,發現總是無法找到故障異常點時,我們必須再度確認是否有位元電性位置(electrical address)與位元物性位置(physical address)不匹配的狀況。此時,宜特科技故障分析實驗室會建議進行Scramble check作業來驗證和確認位元位置的電/物性轉譯。

Scramble check,主要應用於新產品開發初期的驗證。經過與電路設計者討論後,選取特定的字線或位元線甚或特定位元,利用FIB IC電路修補手法將其切斷以製造失效位置,再利用產品測試程式進行失效位置確認,進而確認位元電性位置(electrical address)與位元物性位置(physical address)如何匹配。在Scramble check驗證後,將可排除 SRAM 產品故障分析時找不到正確分析位置的可能性。

本文與長久支持宜特的您分享,如果有需要SRAM故障分析流程表,歡迎與我們聯繫,宜特將提供一張精心製作的圖表,供您參考。歡迎洽詢 +886-3-579-9909 分機 6775施先生(CY) │Email: web_ISE@istgroup.com;marketing_tw@istgroup.com。