發佈日期:2023/11/21 AEC-Q100

發佈單位:iST宜特

隨著電動車搭載更多先進技術,車用半導體元件的可靠度亦變得更加關鍵,為了確保車用元件的可靠度,最新改版的車規AEC-Q100出爐啦,快來看宜特為你畫的重點吧!

AEC-Q100

近年來,新能源車輛,包括油電混合車和純電動車,迅速普及。儘管車市近期遇到了一些逆風,比如特斯拉的財報下滑以及美國汽車製造商的大罷工,甚至有製造商萌生出減緩發展電動車的考慮。但從長期來看,電動車仍是不可忽視的大趨勢。

這一趨勢得益於現代消費者不再僅滿足於車輛的基本功能,他們期望汽車能搭載更先進的技術,如聯網、自動駕駛、共享服務和電動動力等創新功能。這促使汽車製造商積極響應未來汽車趨勢,對於車用電子元件亦日益重視,不僅要求功能安全,還要經過一連串嚴格的可靠度測試,以確保產品在安裝之前無故障或損壞,以滿足新興汽車市場的需求。

那麼,該如何確保車用電子元件可靠度? 汽車電子委員會(Automotive Electronics Council – AEC)近幾年頒布了AEC-Q六大系列標準(點此詳見AEC-Q家族成員)。而本期宜特小學堂,將聚焦於2023年10月AEC宣布的AEC-Q100改版內容,究竟從Version H改版至Version J,有哪些主要差異?以下我們將以三大面向為您剖析新版AEC-Q100。

AEC-Q100

AEC-Q100

一、對特定製程與封裝進行定義

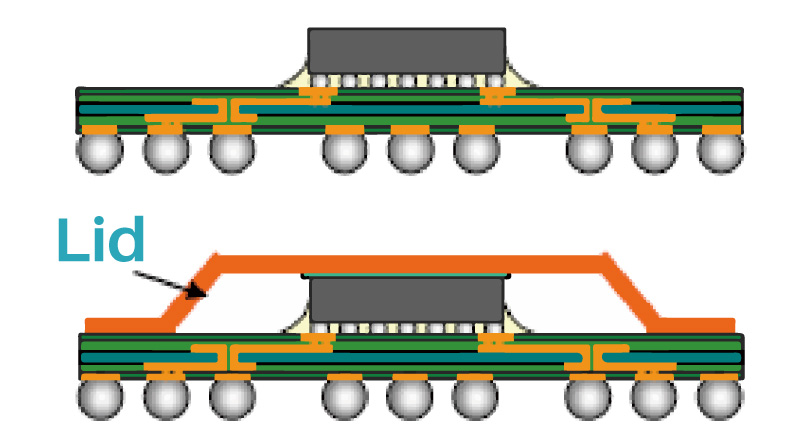

目前,車用半導體元件應用製程,多數為28奈米以上的成熟製程,只有少數車用晶片,如ADAS (先進駕駛輔助系統,Advanced Driver Assistance Systems)等相關應用,則採用14奈米以下的製程。隨著車輛需要處理龐大的數據和資訊反饋,傳統封裝形式如QFP (Quad Flat Package),已無法完全滿足車用高階性能晶片,例如微控制器(MCU)和高效能運算(HPC)等的需求。因此,BGA (球柵陣列,Ball Grid Array)和FC-BGA (覆晶球柵陣列,Flip-Chip Ball Grid Array)等封裝的應用變得更加廣泛。

然而,在上一版AEC-Q100 H版的規範中,並未針對製程與特定封裝形式詳細規範。此次改版,AEC-Q100特別針對28奈米製程、RF頻率元件的ESD耐受程度,以及FC-BGA封裝測試皆進行了定義,以確保這些元件在汽車應用中的可靠性。

此外,為了全面滿足FC-BGA產品的要求,當考慮列入家族產品(Family Product)時,亦新增定義了有關覆晶封裝特定屬性應考慮的衡量準則。值得注意的是,裸晶片產品(Bare Die)和WLCSP (Wafer Level Chip Scale Packaging)不包括在這些屬性清單的範圍內。

二、對故障分析與Mission Profile的應對建議

當車用電子元件在AEC-Q100驗證過程中發生異常、故障,究竟該如何是好呢?是否要一切重頭來過?相信這是大家心中一直以來的困惑。J版規範提及可以有效地透過8D Report (Eight Discipline Methodology,參照JESD 671註)進行故障分析,並建構適當的改善程序,針對改善措施加以驗證並後續追蹤,證明改善措施的有效性及正確性。

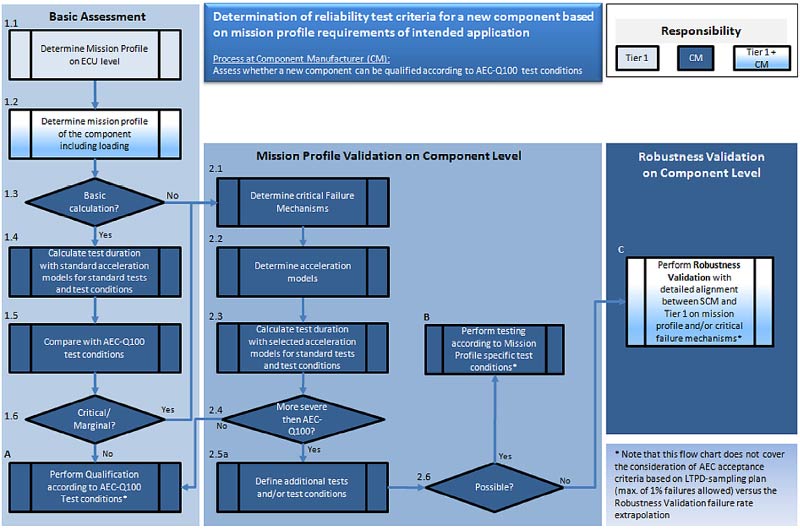

一旦異常點獲得解決,接下來要確保的是,車用電子元件未來能夠在各種複雜和潛在故障事件發生的情況下正常運行,並在預計的使用壽命內(通常是10到15年)維持產品性能。為實現這一目標,可利用Mission Profile流程圖(圖二),以及JESD 94註中提出的KBTM (Knowledge-Based Test Methodology)來確定適當的測試計畫,也可與終端使用者進行溝通,定義出合適的Mission Profile。

三、測試項目與條件的變動

AEC-Q100此次改版,對於PC (Precondition Test)、THB (Temperature Humidity Bias Test)、UHAST (Unbiased Highly Accelerated Stress Test)與SD (Solderability test)測試內容僅些微變動。而在測試項目與條件較大的變動如下所述:

- 車用電子元件中使用的銅打線(Cu wire)是否取得AEC-Q006驗證資料,現已成為元件合格的強制性先決條件。

- 晶圓級可靠度驗證項目將NBTI (Negative Bias Temperature Instability)改為BTI (Bias Temperature Instability),以涵蓋目前CMOS技術的NBTI和PBTI (Positive Bias Temperature Instability)。

- 溫度循環測試TCT (Temperature Cycling) Grade 0測試循環數由2000 cycles下修至1500 cycles,並要求TCT (包括所有溫度等級)結束後要執行超音波掃瞄(Scanning Acoustic Tomography,簡稱SAT檢測)確認晶片內部是否脫層。

- 電源溫度循環測試PTC (Power Temperature Cycling)僅適用於功耗變化≥1瓦,且功率上升時間<0.1秒,預期會導致結溫Tj (Junction Temperature)變化≥40°C的元件。

- 對於元件工作壽命測試HTOL (High Temperature Operating Life)在適用的狀況下,需對電氣參數進行漂移分析(Parametric Drift Analysis),FT測試定義順序為Room→Cold→Hot可替代為Room→Hot→Cold。

- 針對FC-BGA封裝,增加凸塊剪切(Bump Shear Test,簡稱BST)測項。

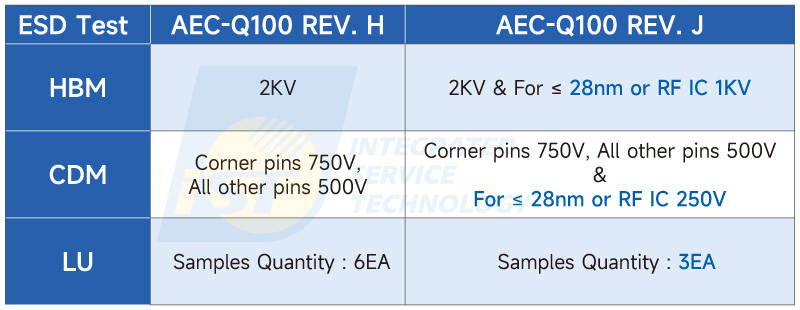

- 因應28奈米與RF晶片對ESD耐受度有別於一般車用晶片,修改了ESD靜電放電測試要求(詳見表一)。

雖然和上一版本已相隔九年,但AEC-Q100此次並未大幅度改版或納入更多新技術,原因在於,汽車產業仍需以「安全、技術成熟」為導向。然而宜特以AEC會員的角色仍可觀察到,為滿足未來汽車智能化和電動化的需求,高階車用晶片市場正迅速成長。此外,這次更新的版本中,我們也意識到隨著不同的環境條件,車用晶片的工作壽命週期需有相應的設計差異。這個觀念也變得越來越深刻且關鍵。想要更進一步了解細節,歡迎洽+886-3-579-9909 分機6403 吳小姐(Sherry) │ Email: web_rce@istgroup.com;marketing_tw@istgroup.com

- 完整AEC-Q100改版文件,請點選此連結。

註:JESD (JEDEC Standards)為JEDEC所發布的標準。