發佈日期:2022/5/3PCB設計

發佈單位:iST宜特

你知道板階可靠度測試結果是Pass或 Fail,PCB測試板設計居然扮演關鍵角色?

我們都知道Package設計工程師,來宜特可靠度驗證實驗室進行板階可靠度(Board Level Reliability;簡稱BLR) 測試前,必須先製作PCB測試板,藉此模擬Package元件組裝於印刷電路板(Printed Circuit Board;簡稱PCB)時,可能出現的錫球焊接問題。(延伸閱讀:板階可靠度BLR對IC設計工程師有多重要)

在實驗過程中,若Package或PCB兩者,只要有其中之一失效,可靠度試驗就宣告Fail。因此,Package與PCB之間,取得平衡點,才能使實驗的壽命最佳化。

不過在BLR測試中,所需的PCB測試板,本身材料、厚度、走線層面等,不僅須要遵照相關國際規範的要求,更是影響可靠度測試結果的關鍵。到底,PCB測試板該如何設計,有哪些Know How呢?

PCB設計

一. 如何開始設計PCB測試板

(一) 選擇實驗欲參照的法規

BLR測試方法可分成五大類,包含熱循環 (Thermal Cycling)、振動(Vibration)、落摔(Drop)、循環式彎曲(Cyclic Bending)、靜態式彎曲(Static Bending)等測試手法。除熱循環(Thermal Cycling)屬溫變類實驗外,其他皆屬於機械類別的試驗。

板階可靠度在消費性產品的國際規範可參考 JEDEC B103/ A104/ B111 /B113、IPC-9701~9704/ 9708,或是各家終端消費型品牌大廠,包括手持式產品、車用電子等類型也都有各自訂定的客戶規範。而客戶BLR測試的依據,可能是基於產業標準或客戶標準,故釐清選用的BLR 測試標準是首要之道,再依據其中不同的實驗項目選擇對應的PCB規範。

不同的實驗規範對於PCB測試板的材料參數、厚度、層數、走線層面、銅線寬度,導通孔(Via)設計方式及表面處理等,都有明確定義,某些規範甚至連板層疊構都有要求,因此設計與製作時必須謹慎,避免違反規範。

(二) 準備菊花鏈(Daisy Chain)的Package與PCB

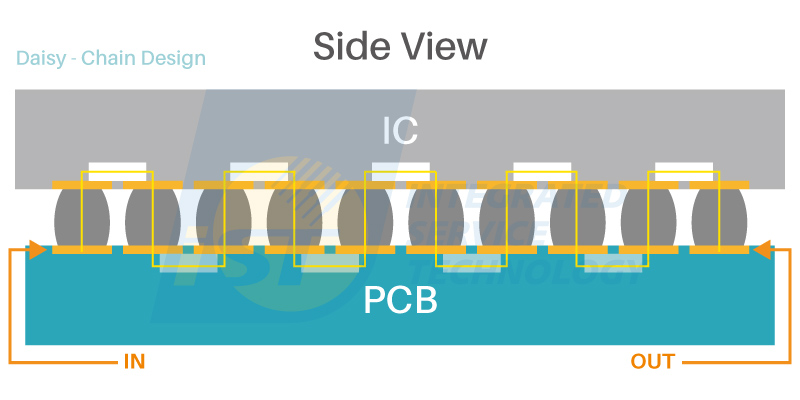

因BLR測試目的是為了解元件上板後的焊點品質,必須透過菊花鍊(Daisy Chain)設計,將待測樣品元件與電路板連結的各個焊點形成網絡,藉此即時監控阻值的變化,可得知各個錫球焊點是否失效,準確擷取失效的時間點,藉此了解各材料所能承受的壽命才可及早進行改善。

- 什麼是 Daisy Chain ?

Daisy Chain線路設計可分成兩部分,一半的線路是設計在Package元件上,另一半則設計在測試板上,當Package元件透過表面黏著(SMT)到測試板時,即可形成一个完整的Daisy Chain。

圖二:Daisy Chain設計

- 什麼是 Daisy Chain ?

二. 那些原因將影響BLR中PCB的可靠度?

以下彙整宜特板階可靠度實驗室十多年遇到的狀況,可歸納下列七項原因。

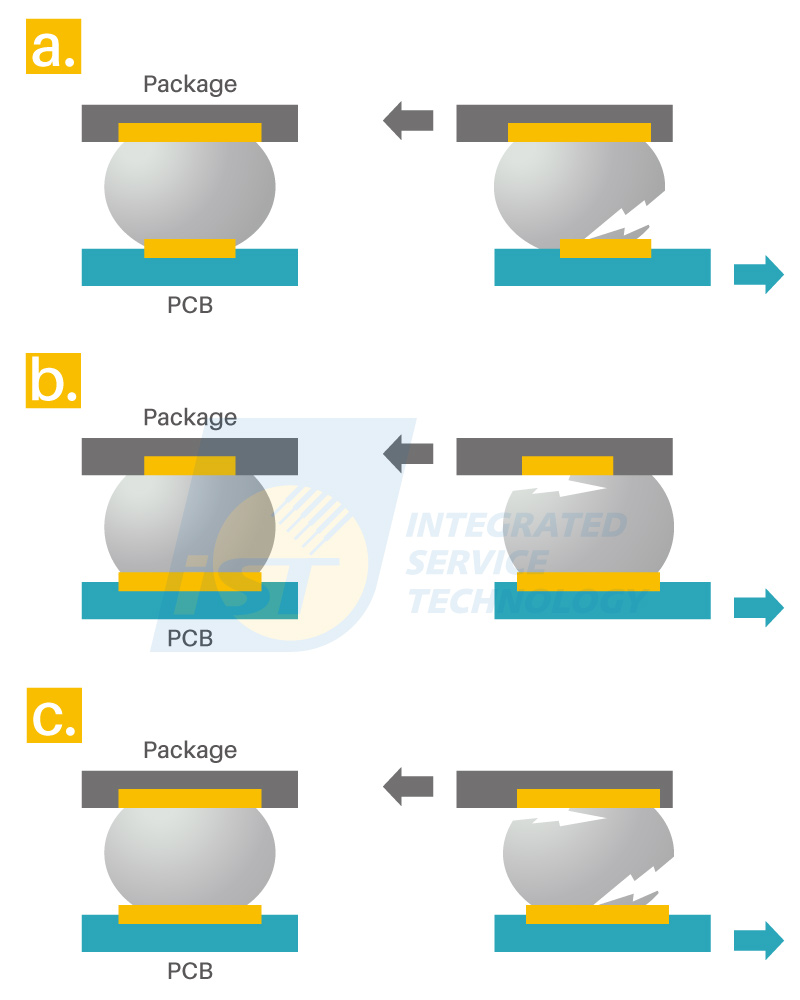

(一) PCB焊墊(Pad)尺寸

試驗時所產生的應力,會使Package上板後最弱的位置先裂開。如下圖三a.為例,若Package端的焊墊(簡稱:Pad)尺寸大於PCB端的,則靠近PCB的位置會最早裂開,反之,結果則相反。而當封裝與 PCB Pad 尺寸 (圖三c.) 一致時,應力分佈最均衡,壽命試驗數據會較佳。

而為了達成此目標,除了PCB設計時,Pad尺寸需與Package一致外,亦需考量板廠的製作誤差,才能上下均衡,進而延長試驗壽命。

圖三:PCB Pad 尺寸的影響,其中圖a. Package Package的Pad較大,錫球容易在靠近PCB處過早破裂(Crack)。圖b. PCB端的Pad較大,導致錫球容易在靠近Package處裂開。圖c. 比例則接近一比一,應力是均衡的。雖錫球上下兩端都有可能裂開,但完全斷裂的時間將被延後。

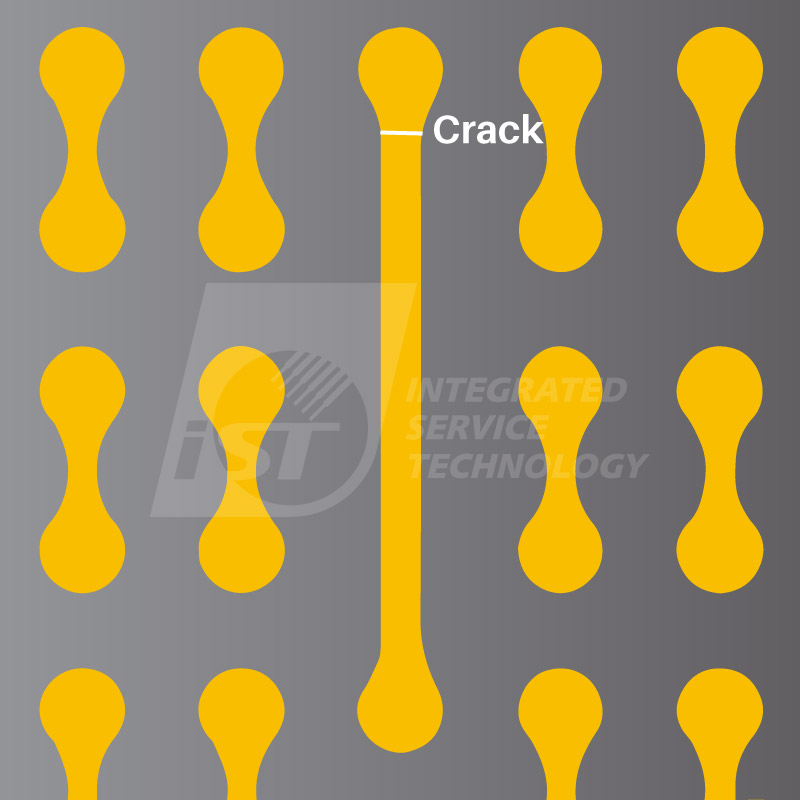

(二) Package Pad分佈狀況

若Package端Pad有空洞或不規則,應力不平均情況下,就會有Crack風險,如圖四裂開Crack位置,最可能發生在缺pad的地方。

圖四: Crack情形

(三) 走線層面

不同試驗類別,對於走線層面的衝擊也不同,必須順應試驗類別選擇走線層面。例如,溫度循環測試與機械類試驗,容易造成Crack的位置就不一樣。所以規範IPC9701,要求走線需在表層;而規範IPC9702,則要求走線在內層。

(四) Package size

外型大顆的Package 通常較重,因此不利機械類的實驗結果。同時Package基板(Substrate)

也容易在受熱後變形 。(五) PCB 翹曲變形

常見造成PCB翹曲變形原因主要有四點,一、須注意板材「熱膨脹係數(CTE)」,避免因PCB異質材料不均勻的收縮,造成嚴重板翹;二、電路板中各層的「導通孔(Via)」將影響PCB變形幅度; 三、 PCB上Package的「重量」,亦是影響板凹因素,以致SMT後PCB形成哭臉或笑臉,使得錫球變形。四、PCB「銅箔面積不均」,熱漲冷縮後造成 PCB 變形。 (延伸閱讀: 掐指算出Warpage翹曲變形量 速解IC上板後空焊早夭異常)

(六) 待測零件擺放至PCB的方向

應以較大應力的方向放置。依據規範JEDEC22-B111、IPC9701要求,Package長短邊的擺放方向應與板框一致。

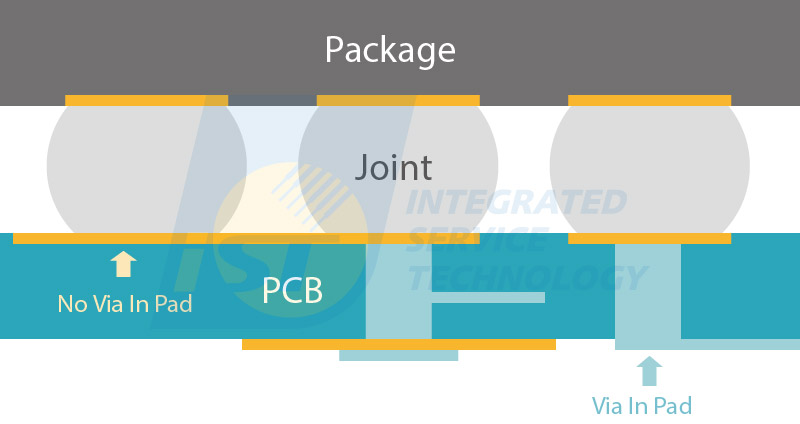

(七) 有無導通孔(Via)

除規範限制外,BGA上,有Via的Pad附著力較好,抵抗整個Pad被拉起的能力,也較無Via優,不過前提是,Via必須電鍍回填。

三. 常見客戶的疑問

(一) 規範JEDEC 新舊版本該如何選擇 ?

您的產品要遵循舊版本JEDEC- B111或新版本JEDEC-B111A,可從Package本體尺寸、成本、以及試驗項目來決定(下表一)。

表一:JDEC新舊版本選擇

(二) 是否可於同一片PCB置具放置不同的package?

答案是不行的,不同的Package尺寸不可混合在同一塊板上,因為會影響板子的動態響應,造成結果難以分析。

(三) 不同實驗是否可共用 PCB測試板?

不同試驗是否可共用同一塊PCB?例如IPC 9701 TCT與IPC9702 Bend 是否可共用? 宜特板階可靠度驗證實驗室的實務經驗中,是「不建議」共用,因不同實驗參照的法規不同,所以在PCB的零件擺放位置、板厚,甚至走線層面等都各有要求,若共用 PCB,將可能導致試驗提早發生失效。

(四) Daisy chain 要怎麼設計最好呢?

最常見的Daisy Chain,是依據Pad的分佈位置區分為不同的Channel,有助於失效偵測及異常分析。

- 可分為一個或多個Daisy Chain進行監測。依PAD分布位置區分為不同的Channel。

- 每个Daisy Chain的輸入和輸出端都必須連接到Connector Pin。

- 封裝上的所有焊点都應被Daisy Chain所覆蓋,包括Ground & Power Pin。

- 盡量增加測試點,提供異常發生時的故障分析(FA)需求。

本文與各位長久以來支持宜特的您,分享BLR PCB經驗,若您想要進一步了解如何根據規範進行PCB測試板製作,請回信給宜特,宜特將手刀奉上一張由宜特精心製作的圖表,讓你一目了然國際規範。請洽+886-3-579-9909 分機 6480 林小姐,Email: web_rce@istgroup.com 或marketing_tw@istgroup.com