發佈日期:2022/4/12SiP故障

發佈單位:iST宜特

MCM/SiP等複雜多晶片結構,如何針對疑似故障晶片進行確認?

如何避開其他元件的干擾,正確判定測試結果?

隨著多媒體影音/高速通訊元件等科技產品,朝向多功能化與IC體積微小化邁進,元件間的系統化整合也被視為未來的重點發展技術。目前業界的封裝技術大多朝SiP (System in Package;系統級構裝)、MCM (Multi Chip Module;多晶片模組) 進行優化。

然而,當IC出現故障時,想分析其中一顆元件或晶粒(Die)的異常狀況,又礙於SiP、MCM內部打線或基板線路互相聯結的複雜關係,將導致進行電性測試時,容易受到其他晶片或元件影響,造成判定困難,甚至無法判定。

該如何解決此狀況呢?本期宜特小學堂,將與您分享解決之道。宜特藉由累積多年厚實的半導體驗證分析技術,研發出IC Repackage移植技術,可從SiP、MCM等多晶片或模組封裝體裏頭,將欲受測之裸Die,無損傷的移植至獨立的封裝測試體,避開其他元件的干擾,進行後續各項電性測試,快速找到IC故障的元兇是誰 (延伸閱讀:如何利用現成晶片變身為測試治具)

SiP故障

一、IC Repackage 移植五步驟

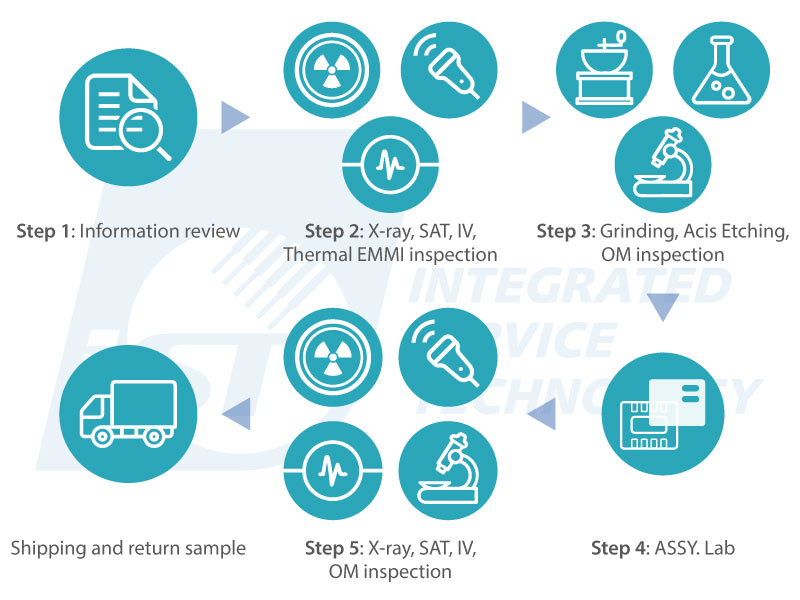

進行IC Repackage 移植,在宜特實驗室需要經過五道步驟(圖一)。

首先,收到待測樣品後,宜特將進行IQC(Incoming Quality Control,樣品進料品質控制),並確認客戶提供的相關資訊,包括利用3D OM檢查外觀有無受損、確認封裝體內Die的數量、目標異常晶片位置與厚度等,這個階段主要目的是確認樣品現況是否吻合客戶反應情形。

第二步驟,將利用X-ray(X射線檢測)或SAT(超音波掃瞄),進一步確認目前樣品有無封裝(Package) 異常,並定位確認需要取出的目標異常晶片位置。 接著,藉由IV電特性量測,來確認封裝體內,客戶指定pin的狀況,同時,視情況,將利用Thermal EMMI (InSb) 來確認亮點與目標異常晶片的關係。

第三步驟,則是利用酸蝕及研磨方式,取出目標異常晶片,並藉由OM(數位顯微鏡),確認晶片有無Crack(裂痕)、Burnout(燒毀)、Chipping(缺口)等問題。

第四步驟,將取出的裸Die,重新打線封裝成客戶要求的Package。最後,宜特可先針對樣品進行IV電特性量測,或是,客戶也攜回該顆重新封裝過後的IC,至自家廠內進行功能性電特性量測。

圖一:宜特科技實驗室 IC Repackage移植五步驟

二、IC Repackage 移植經典案例

■ 取出SiP中的目標異常Die,製備成wBGA

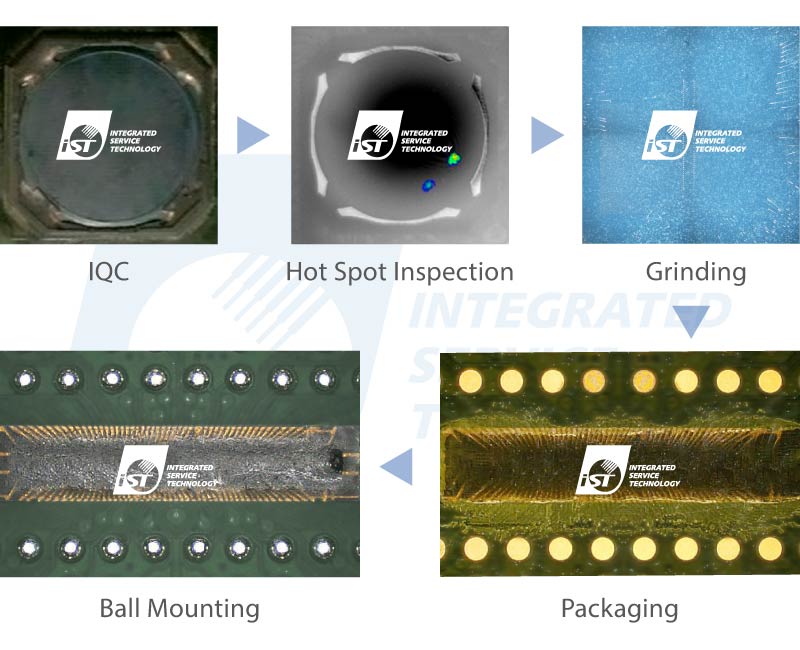

圖二為SiP樣品,宜特科技透過Repackage移植技術,將其中的目標異常裸Die取出,進行樣品製備,移植成wBGA (window Ball Grid Array) 封裝形式。藉此,客戶即可避開其他元件的干擾,針對該顆wBGA進行後續ATE(Automatic Test Equipment),確認異常位置。

圖二:移植SIP裏頭的目標裸Die,樣品製備為wBGA封裝形式,順利進行後續各項測試。

■ 從Module(模組)中取出元件,進行植球

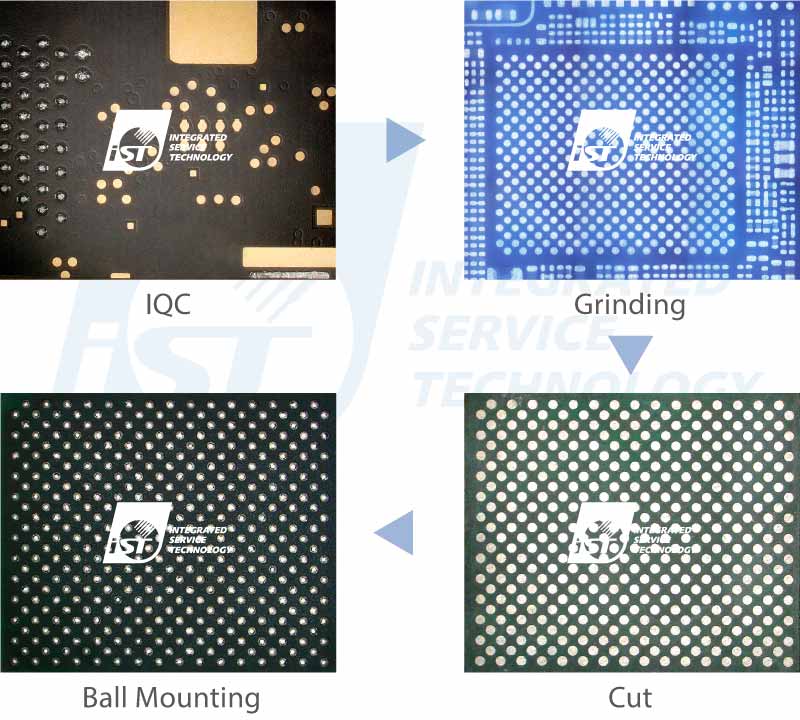

當Module (模組)中有多顆IC或元件時,宜特實驗室透過研磨或切割,將目標元件從Module中取出,接著進行植球服務,讓客戶可以取回至自家廠內進行各項測試,釐清相關故障原因。

下圖為從Module(模組)中取出我們的目標BGA IC,經過尺寸量測及植球後,便於客戶後續測試。

圖三:取出Module內的目標元件,經植球後,即可回到客戶廠內測試。

本文與各位長久以來支持宜特的您,分享經驗,若您有關於IC Repackage相關知識或需求想要更進一步了解,歡迎洽詢+886-3-579-9909 分機6755歐先生│Email: IST_FA_IAD@istgroup.com / marketing_tw@istgroup.com