發佈日期:2019/4/25

發佈單位:iST宜特

V2X技術、5G通信標準的加持,讓車聯網的普及指日可待,

亦使得高頻通訊晶片朝SiP、MCM、Fan-in/Fan-out先進封裝邁進。

在車電可靠度上面,將會面臨什麼挑戰?該如何解?

隨著車聯網發展,先進智慧車用電子產品成為近年來發展的主要趨勢,尤其對半導體產業而言,車用電子更是下一個新興戰場。過去幾年仍在紙上談兵階段的ADAS,在2018年已有部分車廠的中階車款開始配備,2019年預計會進一步普及。

在傳統汽車產業,以往不會將最先進的技術、製程等放入最暢銷的車款上,而是把最成熟、可靠度品質最佳的產品導入,「穩定度」一直是最重要考量,此一考量至今仍然存在。不過隨著車聯網、AI等各種技術的導入,「效能需求」也開始浮現,此一趨勢也將對IC封裝形式帶來改變。

過去半導體的封裝無非是用現已穩定成熟的BGA、QFP、SOP等包裝,不過在自駕車市場需求驅動下所延伸出的AI、HPC需求及C-V2X(蜂窩車聯網,Cellular V2X) 、DSRC(專用短程通訊,Dedicated Short Range Communication)等車聯網通訊標準技術,這些封裝技術已難以滿足新世代高速運算及高速傳輸速度需求,多晶片模組(Multi-Chip Module;MCM)、系統級封裝(System in Package;SiP) 或Fan-in/Fan-out等先進封裝成為必然趨勢,而這些先進封裝技術也必須面臨「品質」、「安全」與「可靠度」等3大挑戰。

在「品質」與「安全」上,目前在汽車產業都已有完整規範,品質方面主要是IATF 16949(延伸閱讀: 了解三大面向,順利取得IATF 16949汽車品質管理系統證書),部分歐洲車廠會要求VDA6.3,量產階段也有新標準AQP,安全性方面則是ISO 26262。(延伸閱讀: 進入電動車供應鏈必備-國際可靠度品質車規五步驟一次解析)

而在「可靠度」上,必須從2R階段強化-CLR(元件可靠度Component Level Reliability)、BLR(板階可靠度Board Level Reliability)。這2個階段代表IC從元件到元件上板階段。若這2個階段都可通過考驗,就適於應用在汽車環境。本月宜特小學堂,將從CLR與BLR,帶各位了解先進封裝在此兩階段的挑戰與解決之道。

一、 先進封裝在CLR階段三大挑戰

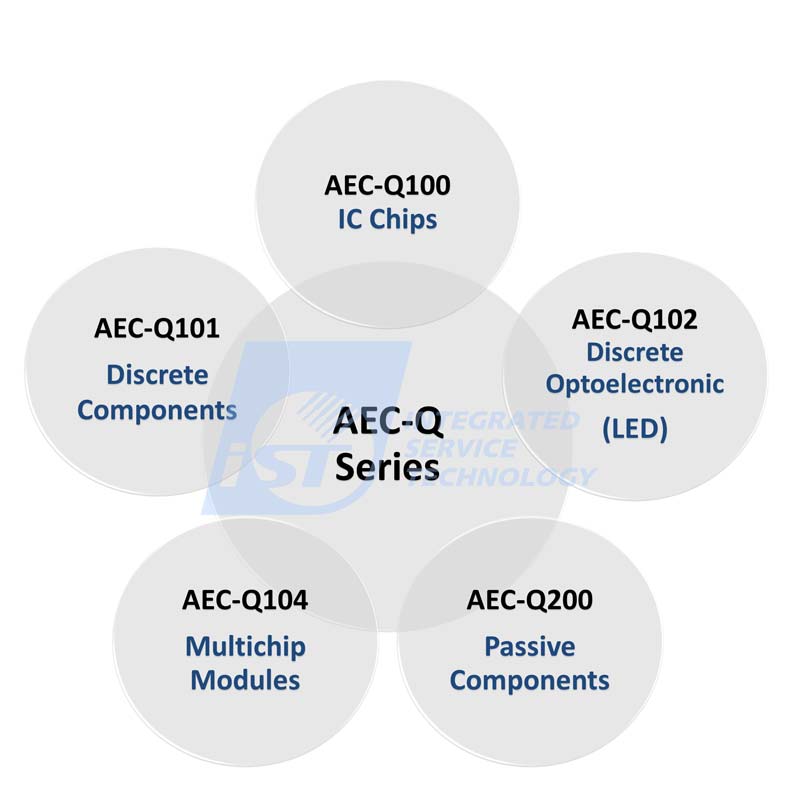

在元件方面,國際汽車電子協會(Automotive Electronics Council,簡稱AEC)早已針對IC晶片、離散元件、離散光電元件、被動元件制定出AEC-Q100、AEC-Q101、AEC-Q102與AEC-Q200等車用規範(參見圖一),元件要符合這些規範,必須克服「散熱」(Heat Dissipation)、翹曲(Warpage)與連續性測試(Sequential Stress Tests)3大問題。

(一) 散熱 (Heat Dissipation)

「熱」永遠是可靠度的第一殺手,而車用系統近年來對效能的需求增加,高運算帶來高耗能,再加上車內的嚴苛環境,IC的可靠度將大受威脅,因此如何在效能與耗電中取得平衡,是車電IC設計重點。

(二) 翹曲(Warpage )

另一個現在最常見也是最嚴重的問題是IC封裝體的翹曲。為因應高速傳輸需求,車用IC的封裝方式逐漸由BGA轉變為MCM/SiP,由於多晶片封裝整合了多種晶片及主被動零件/PCB,各種材質所組合出的複雜的熱膨脹係數(CTE),且在溫度劇變的汽車應用環境下其封裝體及焊接點非常容易產生翹曲變形,進而產生可靠度問題,而且此一狀況不只出現在IC元件,電路板也會遇到。

特別是高頻,是現在車用系統常見的設計,未來5G上路後更會成為必要需求,高頻系統的電路板必須選用特殊材質,不過此一材質在超過Tg的溫度時膨脹係數(CTE)會高達到4倍,翹曲問題會非常嚴重。

(三) 連續性測試(Sequential Stress Tests)

最後的挑戰則來自於新規範AEC-Q104(延伸閱讀: 六大重點,秒懂車用多晶片模組AEC-Q104規範),此規範的其一重點在於連續性測試(Sequential Stress Tests),連續性測試在模組端已行之有年,不過在2018年,AEC將此規範延伸到元件端。AEC-Q104的考量點在於車子運作時,所有的狀況都是連續發生,車體系統必須承受複合應用,因此元件部分也必須具備因應連續環境的能力。

過去大多以單一晶片進行封裝,材質與結構較為單純,只要逐一測試即可,但在新世代的先進封裝MCM、SiP中,所包含的IC種類多,組合起來的特性也不一樣,在車體運作時,有可能會因連續狀況導致晶片失效,AEC-Q104即是規定晶片在測試過程中,每一連續性的環節都必須通過。

舉例來說,以往高溫壽命試驗(HTOL)與溫度衝擊(Thermal Shock)這兩個項目都是分開測試,AEC-Q104則是要先做高溫壽命試驗,通過後緊接著做溫度衝擊,全部都測完後才算通過,這不但拉長了驗證時間,也讓驗證難度再提升,雖然AEC-Q104並非強制性,不過絕大多數車廠都會要求,因此有意投入車用領域的廠商,仍必須通過此規範。

二、 先進封裝在BLR階段的挑戰

(一) 翹曲(Warpage)

多晶片模組、系統級封裝與Fan-in/Fan-out等先進封裝透過堆疊兩個或更多不同功能晶片,並以雷射垂直導通孔(Through Silicon Via; TSV)進行結合,這樣的元件使用的材料相當複雜且多元,當遇到溫度的變化因材料本身熱膨脹係數不同(CTE)就會產生翹曲(Warpage),若選擇不好的材料有可能翹曲過大而導致後續SMT電路板的結合異常。

另一方面,5G技術針對較高頻電路板材料也是挑戰之一。電路板應用於車載中除了必須考量訊號衰減的因素外,更需要關心的是在高溫的環境中是否也有翹曲的狀況發生。

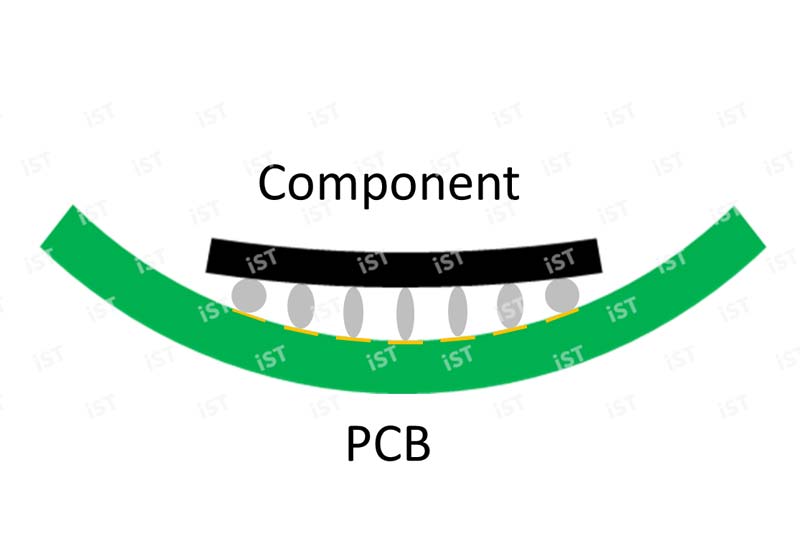

圖二:元件與電路板都有可能有翹曲發生 進而影響後續SMT焊接品質。

不正常的翹曲的確會造成可靠度驗證的風險,導致元件與電路板在實際驗證時會有極大落差。過去的作法是先按規範實作,設計出電路板,客戶端有問題再逐一調整修正,直到做出可實際應用的電路板,而這種作法勢必耗費大量的人力與時間資源。

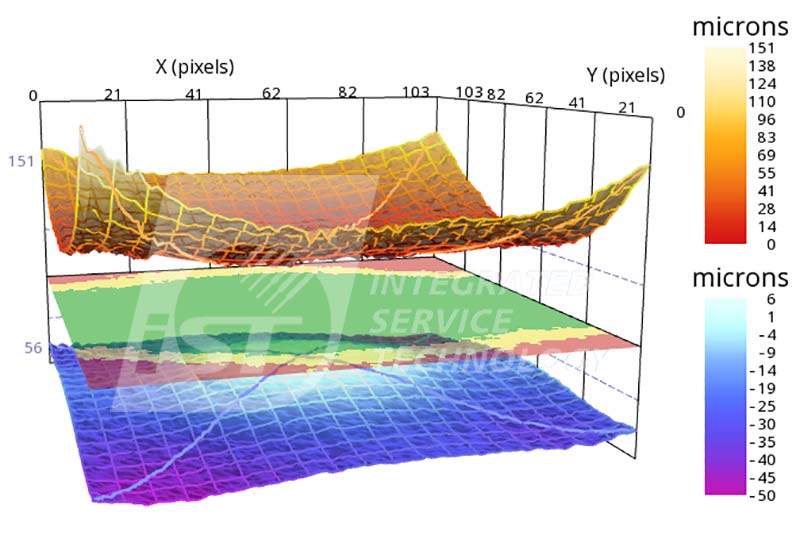

三、 先進封裝在車用可靠度的解決之道

翹曲,是先進封裝在車用可靠度共通遇到的難題。為解決車用系統中元件與電路板的各種問題,在翹曲(Warpage)上,宜特特別建置翹曲測試設備,未來能為客戶在表面黏著技術(SMT)前,就針對元件與電路板進行翹曲量測,確保在SMT過程中能保有良好的焊接品質(參見圖三),如此可避免因不良焊接品質導致影響可靠度驗證以及不必要的成本開銷。

圖三: SMT上板前,可針對元件與PCB進行模擬分析,預先了解Warpage情形

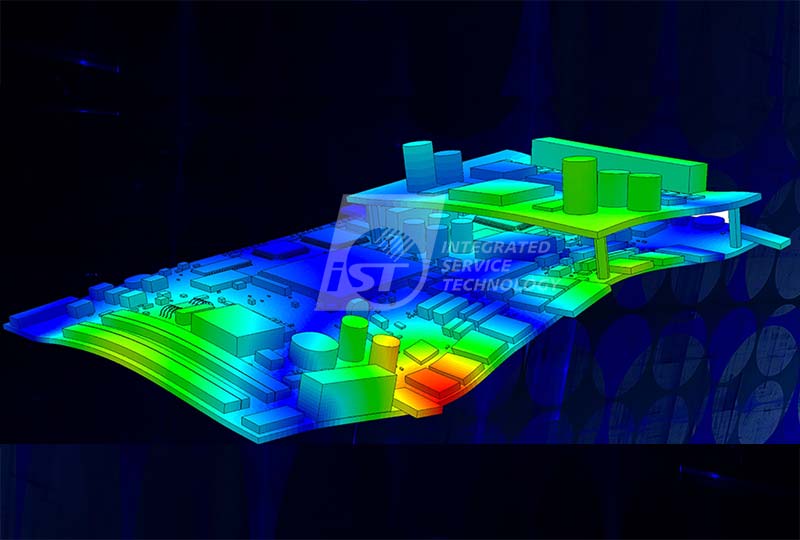

另外,宜特與美國DFR Solutions(簡稱DFR)公司合作導入模擬軟體,DFR是汽車產業著名的顧問公司,所設計的Sherlock軟體已被歐美大型車廠採用,而宜特就以此軟體運行過去累積的大量數據,找出各種實際應力參數,讓電路板設計更接近實際應用狀況(參見圖四)。Sherlock是可靠度測試前的分析工具,可針對材料熱膨脹係數、翹曲延展性以及外界產生應力進行驗證。另外Sherlock也能與產業中常用的CAE軟體進行接合,大幅降低分析時間。

圖四:藉由CAR軟體,了解產品的應力分布與形變量,可在測試前,預先了解產品可能會有什麼風險

從2018年開始,ADAS的普及速度加快,這也衍生出半導體產業的新商機,目前台灣高科技業者也開始投入發展,不過車用系統無論是設計思維、產業生態或標準規範,都與消費性產品不同,尤其在驗證部分更有極大差異,宜特在汽車電子領域有多年經驗,藉由過去所建立的經驗,將可有效協助客戶導正產品研發方向,同時縮短產品上市時間,強化自身的市場競爭力。

本文與各位長久以來支持宜特的您,分享經驗,若您對先進封裝在汽車電子可靠度驗證上,想要更進一步了解細節,歡迎洽詢+886-3-579-9909 分機 6406 莊先生(Daniel) │Email: web_BLR@istgroup.com 。