發佈日期:2026/04/14 矽光子CPO故障分析

發佈單位:iST宜特

矽光子晶片一旦經過封裝後便難以進行重工製程,您該如何確保昂貴的ASIC晶片不會因為一顆微小的PIC光學元件失效而整顆報廢?本文將拆解矽光子PIC五大部件最具代表性的故障模式,突破量產「盲對準」的最後一哩路。

矽光子CPO故障分析

矽光子CPO故障分析

NVIDIA黃仁勳預期 2027 年 AI 基礎設施將達兆元規模,但傳輸瓶頸導致 GPU 使用率低於 20%。為突破限制,NVIDIA 與台積電積極佈局 CPO(共同封裝光學),透過 COUPE 技術實現光電 3D 異質整合,預計 2026 年邁入量產元年。

然而,從「電」轉「光」是全新的戰場。工程師面臨的不只是漏電,更是漏光、光耦合偏差與訊號衰減等棘手失效。當設計走向實體產品,最關鍵的挑戰,便是如何透過嚴謹的驗證,確保這項高價值技術的可靠度與壽命。

之前我們已從矽光子元件組成與決定效能的關鍵(閱讀更多:「光」革新突破半導體極限 矽光子晶片即將上陣),進而分享對應的解決方案(閱讀更多:矽光子開發為何這麼難?驗證手法是關鍵),以及如何突破矽光子量產的核心難關(閱讀更多:矽光子CPO量產見曙光!從「漏電」到「漏光」如何迎刃而解?)。

本文將繼續帶領IC工程師轉換視角,從看診電性晶片的「神經內科醫生」變身為治療矽光子疾病的「眼科醫生」。我們將針對光子積體電路(PIC)的五大關鍵部件,詳細剖析其操作原理、常見故障模式以及尖端的故障分析(Failure Analysis, FA)技術,協助產業界打通矽光子量產的任督二脈。

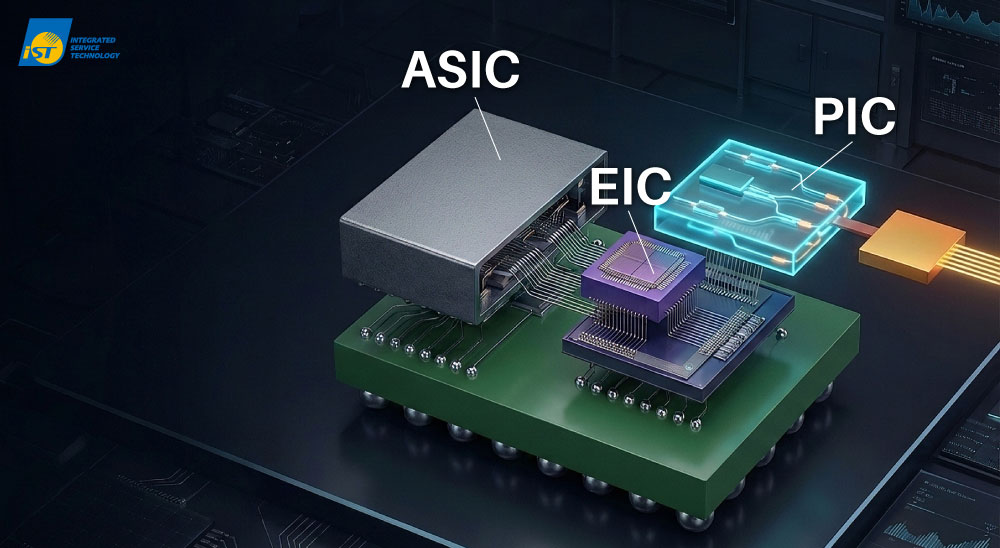

一、CPO三大核心架構:從「離散外掛」走向「異質整合」

二、PIC五大關鍵部件與故障模式

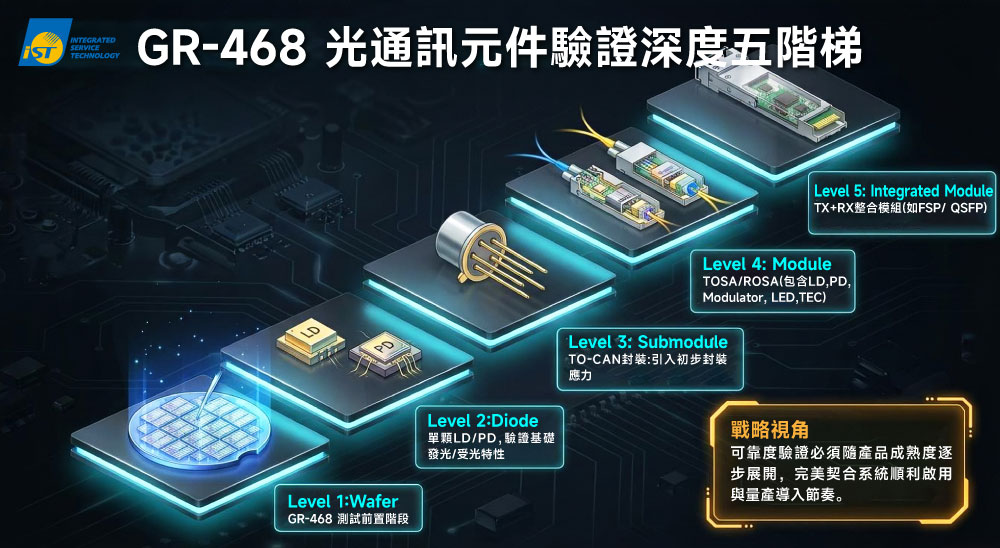

相較於業界已熟稔的 ASIC 與 EIC 故障模式,PIC (光子積體電路) 才是 CPO 驗證中最陌生的戰場。 PIC 內部五大關鍵部件各有獨特的物理機制,也衍生出截然不同的失效路徑;要精準定位並排除這些微觀病灶,極為仰賴尖端的故障分析(FA)技術,才能在量產前完成最後的風險收斂。

圖二:PIC晶片五大關鍵部件示意圖,每個部件都有獨特的物理機制與故障模式

(圖片來源: iST宜特-AI輔助生成製作)(一)光柵耦合器 (Grating Couplers, GC) :

- 操作原理:

利用溝槽結構讓外部光纖以特定角度耦合進入晶片波導。需精準計算角度與尺寸,直接影響收光效率與偏振選擇性。 - 常見故障模式:

對準偏差、製程殘留物或環境掉落塵粒導致表面型態變異,或應力造成的物理損壞,皆會引發漏光或波長偏移。 - 分析技術:

宜特實驗室可透過掃描式電子顯微鏡(SEM)、能量色散X射線光譜儀(EDX)、聚焦離子束(FIB)與穿透式電子顯微鏡(TEM),進行微觀缺陷分析,並透過切片檢查確認雷射與光柵耦合的實體完整性。

(二)光波導 (Waveguides, WG) :

- 操作原理:

負責光傳輸的通道。利用核心與包覆材料的折射率差形成「全反射」,將光束限制在通道內。矽、氮化矽或碳化矽均為常用材料。 - 常見故障模式:

需嚴格檢視材料吸收率,過高將導致傳輸衰減;波導側壁粗糙會引發散射損耗;此外,熱穩定性對折射率的影響亦至關重要。 - 分析技術:

宜特透過精細的切片分析(Cross-section),以觀察波導傳輸通道的結構尺寸是否合乎設計,並檢視是否有導致光訊號散失的結構變異或缺陷。

(三)熱調諧器 (Heaters) :

- 操作原理:

藉由電流產生熱能改變波導局部溫度,引發折射率改變以微調相位。常用材質包括鈦 (Ti)、鎢 (W) 或氮化鈦 (TiN)。。 - 常見故障模式:

導線間距過近或絕緣不良易導致漏電,甚至遭受 ESD 靜電擊穿造成結構燒毀,或因熱隔離 (Thermal Isolation) 不佳干擾鄰近元件。 - 分析技術:

宜特針對漏電點進行橫截面檢查,並配合精密層次去除 (Delayer) 分析,逐層尋找燒毀或漏電的確切位置。

(四)PN接面調變器 (PN Junction Modulator) :

- 操作原理:

對 PN 接面施加逆向偏壓以改變空乏區大小,進而調整折射率與光速。透過干涉原理,將「電訊號 (0 與 1)」轉化為「光訊號」。 - 常見故障模式:

高溫引發的暫態失效 (熱飄移)、ESD 永久性擊穿,以及離子植入濃度變異導致調變效率低下。 - 分析技術:

透過掃描電容顯微鏡(SCM)或原子力顯微鏡(AFM),將載子濃度與摻雜輪廓具象化,以確認是否符合原始設計。當然,PN接面的切片檢查也是不可或缺的一環。

(五)鍺光電偵測器 (Ge Photodiodes, PD) :

- 操作原理:

負責將光訊號重新轉回電訊號。業界常於矽製程中加入鍺 (Ge) 元素,以大幅提升對特定波長光訊號的感測靈敏度。 - 常見故障模式:

最大的致命傷是暗電流(Dark Current)過高。這通常源於磊晶生長的晶格缺陷,殘留金(Au)、鋁(Al)等金屬微污染,皆可能形成漏電路徑。其他亦可因受外在熱應力破壞或因長期硬體操作不當或突發大電流導致元件失效或實體燒毀。 - 分析技術:

鍺光電偵測器的分析極具挑戰性。宜特科技透過電子束誘發電流(EBIC)技術進行高解析度的電性故障定位,再輔以穿透式電子顯微鏡(TEM)、能量色散X射線光譜儀(EDX)以及二次離子質譜儀(SIMS)進行深度的晶格缺陷與金屬污染分析,確保找出導致鍺光電偵測器失效的真兇。

- 操作原理:

三、測試與量產的終極難關:盲對準與KGD的數學陷阱

在推進矽光子量產時,工程師會遭遇有別於傳統IC製造的挑戰,這不僅是物理極限的對抗,更是一場關於成本與良率的數學陷阱。

(一)光耦合的「盲操作」:

要把光順利打進比頭髮還細的波導,對準誤差必須控制在0.5微米以內。傳統測試需反覆調焦與換角,極低的產出率(Throughput)與高昂時間成本,直接拖累產品上市時程。

(二)KGD(Known Good Die)的良率乘法陷阱:

在異質整合架構下,,總良率是各組件的「乘積」。若在封裝後才發現 PIC 失效,損失的不只是廉價元件,更是與其封裝在一起、價值數千美金的高階 ASIC。這種「小零件拖垮大晶片」的風險,是讓毛利歸零的致命傷。

(三)傳統推測法的極限:

過去的光學晶圓測試(OWAT)多依賴反射量測,僅能得知「總體插入損耗」。工程師無法在封裝前判定確切光損數值與病灶,導致風險一路被帶入最終產線。

四、 驗證標準與突破:從「推測」到「可視化」精準量測

矽光子與 CPO 是突破 AI 算力瓶頸的關鍵,但複雜的故障分析路徑與良率陷阱,唯有透過精準的「定性與定量」分析才能化解。若您有相關需求。立即回信與我們聯繫,讓我們一起突破矽光子的研發瓶頸!

歡迎洽詢+886-3-5799909 分機1065 陳小姐│Email: marketing_tw@istgroup.com