發佈日期:2025/2/18FIB電路修補

發佈單位:iST宜特

切錯點、接錯線,讓你胃食道逆流嗎?本期宜特小學堂,帶您一次掌握FIB(Focused Ion Beam)電路修補全攻略!幫助工程師跳脫debug地獄,高效完成設計驗證。

FIB電路修補

在IC設計這條路上,就算模擬結果看起來完美得像神作,一上晶片還是可能冒出讓人崩潰的電路異常。這不只是花錢重投片的問題,更是會把專案時程拖到天荒地老,客戶追殺。更慘的是,碰到電路有問題時,工程師最常面對的困擾就是:找不到defect,完全搞不清楚要接哪條線、切哪個位置,debug起來簡直讓人懷疑人生。

這時候,FIB(Focused Ion Beam)電路修補技術就像救世主一樣登場了!它可以快速又靈活地幫你修電路,用最少的成本和時間完成設計驗證,不再掉進無限循環的debug地獄。

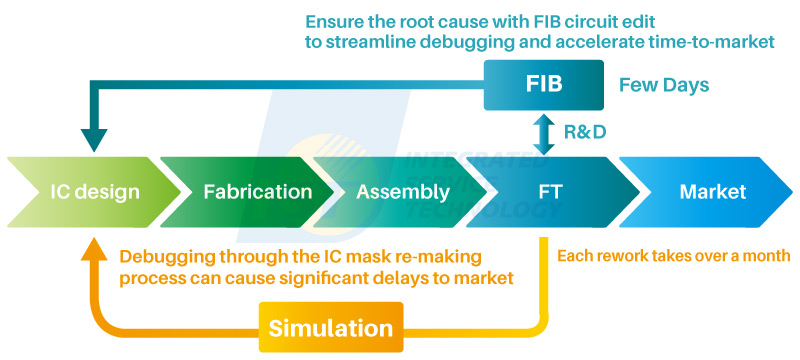

作為台灣首家推出FIB電路修補服務的民營實驗室,宜特科技FIB電路修補服務,可節省每顆IC晶片在設計階段三到六星期的研發時間,並節省上千萬重新下光罩的經費,讓產品可以快速上市。宜特FIB實驗室更以24小時全年無休的服務,協助客戶產品除錯,快速找出問題癥結。

之前的宜特小學堂,我們分享了如何進行先進製程IC的FIB(Focused Ion Beam)電路修補,介紹了晶背修改的多項優勢,也展示了一些高難度的修改案例(閱讀更多:先進製程的IC,該如何從晶背進行FIB電路修補? 和 5奈米晶片FIB電路修補 到底難在哪)。本期宜特小學堂,我們將不藏私分享宜特30年的FIB電路修補經驗,幫助您全面了解這項關鍵技術,讓debug加速跑,設計效率也跟著直線飆升!

FIB電路修補

FIB電路修補

一、FIB 原理簡介

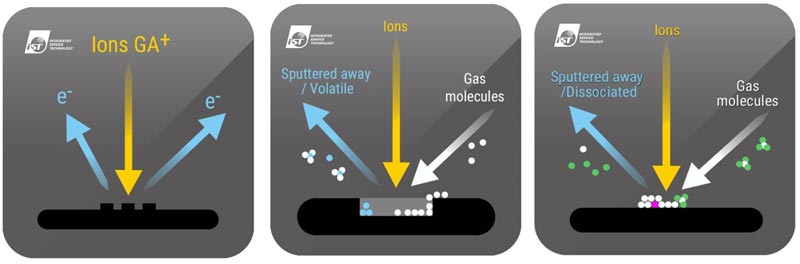

FIB (Focus Ion Beam)聚焦離子束電子顯微鏡,是利用鎵(GA+)離子源透過電場牽引成離子束,收集高速碰撞樣品表面產生的二次離子、電子後成像;在離子轟擊過程中利用不同氣體的注入,對晶片上各種材料進行選擇性地加速或減緩蝕刻,以及沉積導電和介電絕緣材料,達到修改電路的目的,搭配CAD導航系統輔助,準確的定位目標,提高電路修補精準度。

二、為什麼要進行FIB電路修補?

就像醫生透過外科顯微手術精確地解決病人的身體缺陷,改善其健康狀況,宜特FIB實驗室透過專業和細緻的IC電路修補,能有效地在晶片下線(tape out)前確認問題所在,可節省高額重新投片成本,加快原型驗證的速度,縮短上市時間。FIB電路修補技術也可協助客戶在開發時程緊迫的情況下,進行少量改版量產,再將樣品送交終端客戶進行驗證,成功取得先機,爭取到訂單。

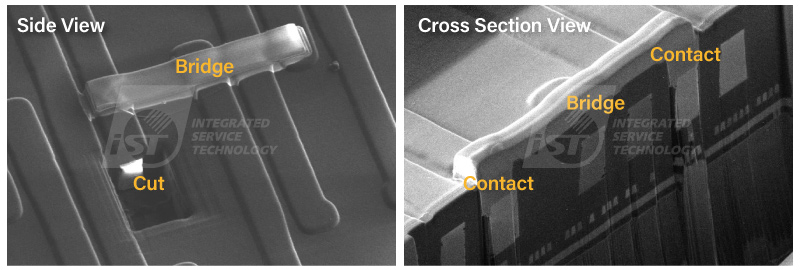

FIB技術利用蝕刻移除絕緣層及金屬層,並透過沉積金屬材料重新連接到其他路徑,這一過程能夠精確地依照客戶需求,並進行測試確認電路中的問題。

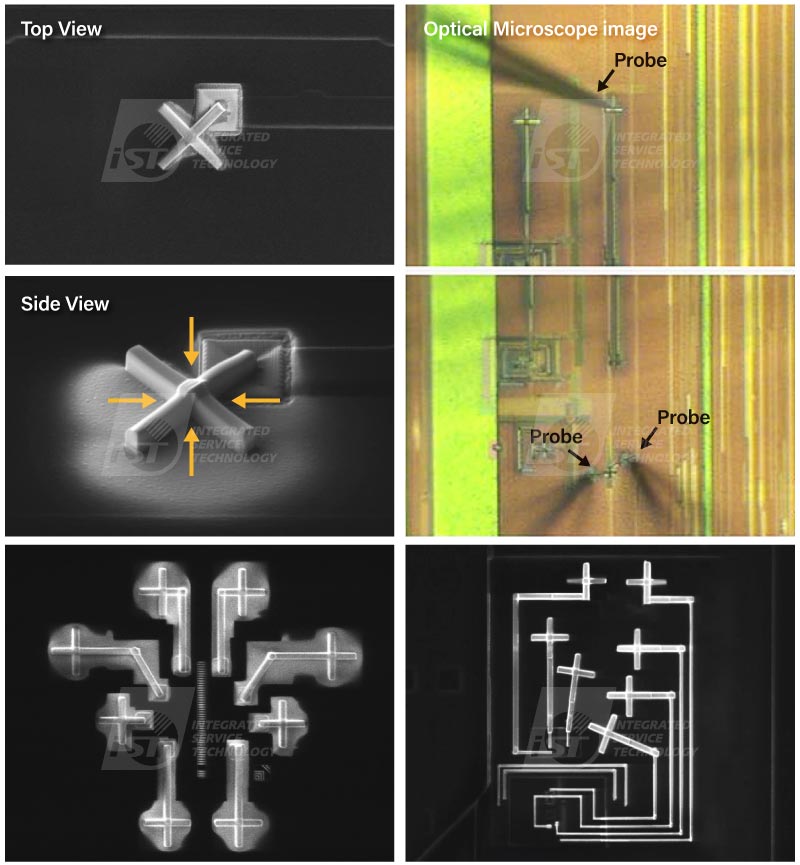

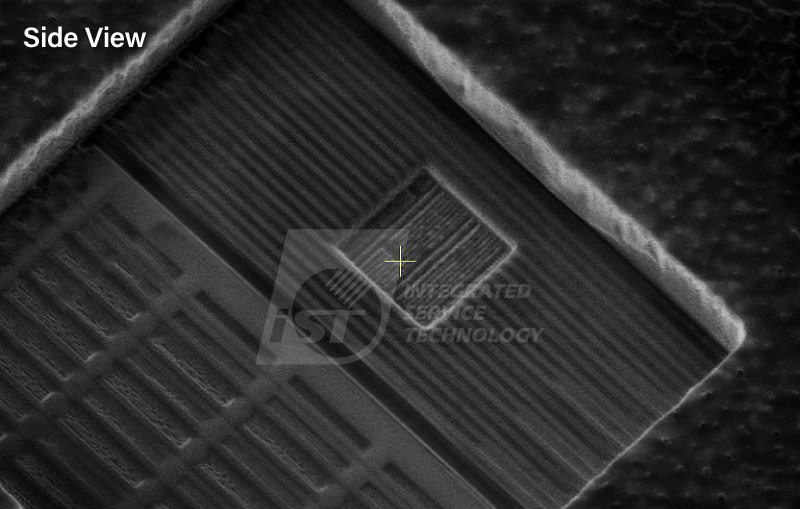

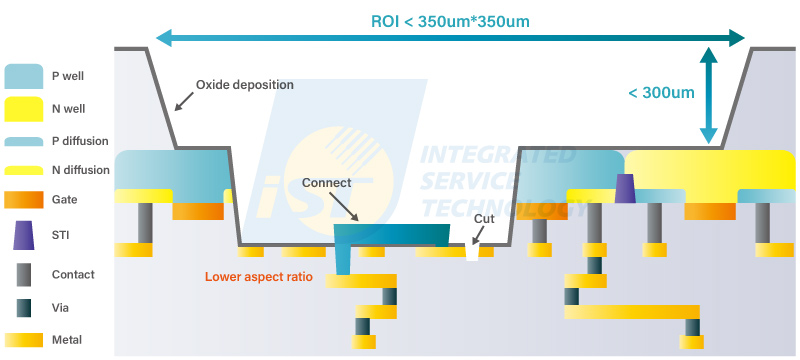

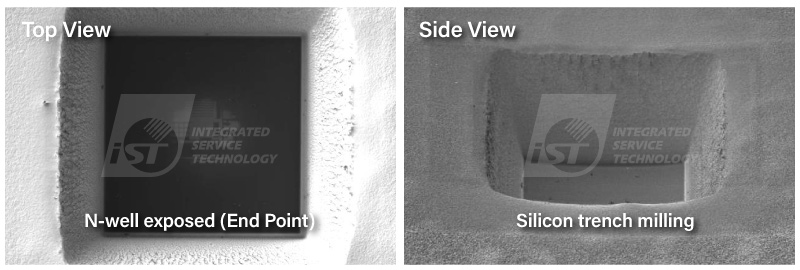

透過剖面圖(Cross-section view),我們可以清楚地了解使用聚焦離子束這一技術能夠精確去除表層材料,暴露出目標區域的金屬層,緊接著將金屬材料沉積填充在接觸點(contact)上並在晶片表面進行橋接,實現電路的重新連接。後續便可進行測試,真實驗證電路的功能是否符合模擬結果。

此外,根據條件的需求,也能執行更複雜的電路重構,進一步擴大解決方案的範圍,客戶依據測試結果確認電路中的缺陷,滿足在電路除錯上的各種需求。

三、宜特FIB電路修補的各種廣泛應用

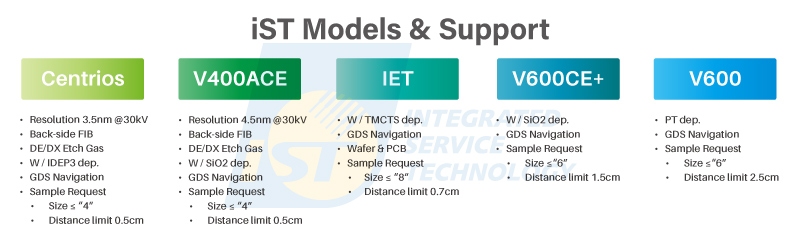

宜特的FIB電路修補技術已突破3nm製程,並提供晶片正面與背面電路修補服務。設備類型多元且數量充足(表一),不僅能滿足高產能需求,還能靈活提供多樣化解決方案,確保穩定的高良率與快速交期。此外,宜特擁有豐富經驗的技術團隊,專精於多種設備操作,並獨家支援8吋晶圓不破片的電路修補服務,這項技術是台灣市場中的唯一選項。

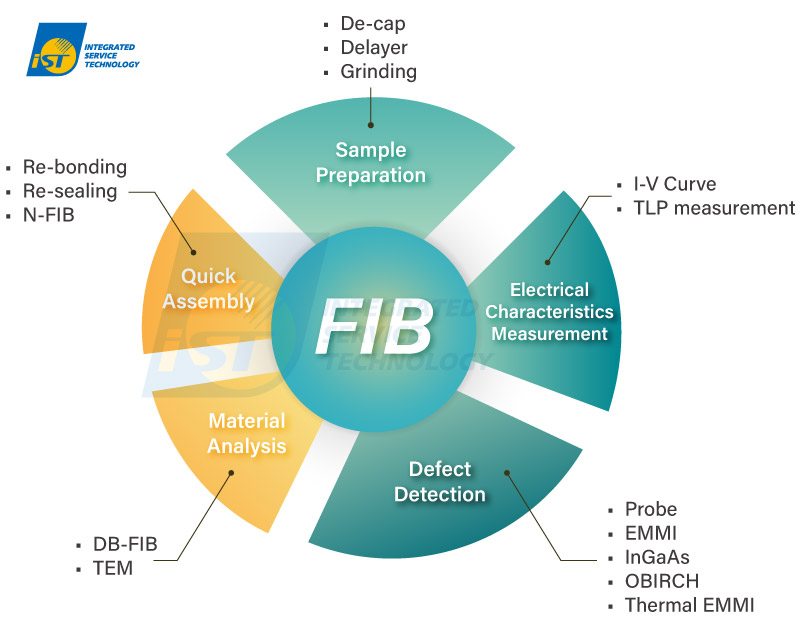

由圖五可見,FIB電路修補後可接續進行電性量測、故障點偵測、材料分析和快速封裝等實驗,以下我們將一一分述FIB的各種廣泛應用。

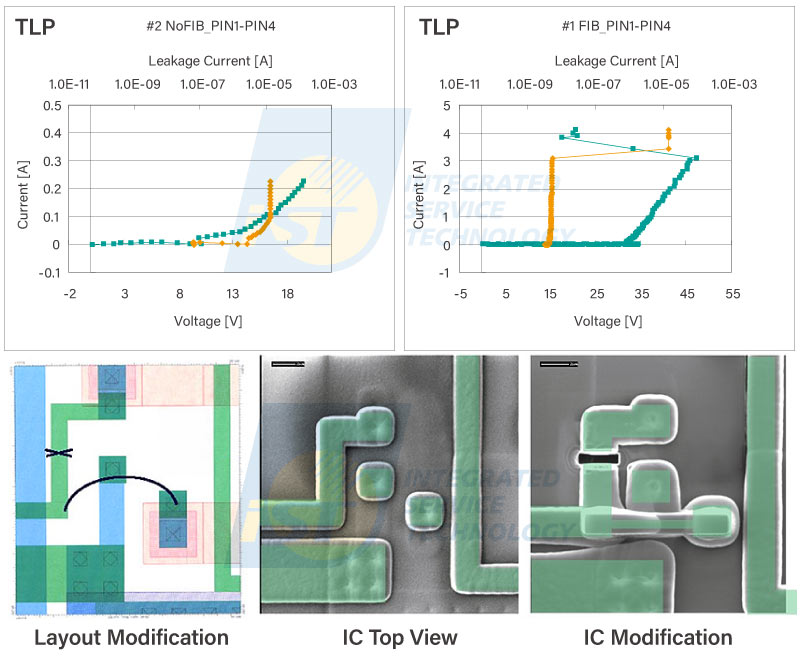

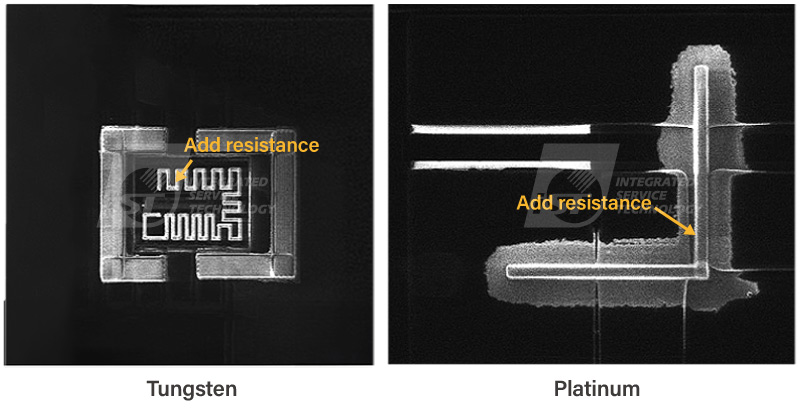

(一)利用FIB技術沉積金屬材料進行電阻調整

FIB 電路修補技術可以利用沉積金屬材料進行電路連接,然而,進一步的應用,亦可以根據客戶需求,在兩個電路節點之間,透過沉積具有不同電阻係數的金屬,例如鎢(Tunsten)或鉑(Platinum),來控制金屬的連接長度,達到調整電阻值的目的。此法可用來模擬不同電阻對電路性能的影響,後續亦可以進行波形(I-V Curve)、ESD等相關故障分析實驗量測。

(二)宜特獨特客製化的FIB PAD設計幫助IC後續順利進行電性測試

宜特的FIB Pad設計為十字形狀,除了能夠使探針穩定地頂住任一內角,防止針座滑動,並且擁有多向角度調整的可能性,方便在接觸不良時,重新調整針座位置與方向以達到最佳接觸效果,進而重複使用。不僅提高了操作的穩定性,也延長使用壽命。

並可進一步根據客戶需求製作更多且更複雜的FIB Pad,利用點針技術準確地擷取訊號,測試該區域電路是否符合研發設計要求,及時發現進而定位缺陷,後續可再進一步進行電路修補,改善問題;或是接續亮點分析,針對異常位置進行剖面(cross section) FIB或TEM分析,確認製程缺陷。

此外,宜特的FIB 實驗室建置介電絕緣材料,即使是晶圓半成品或經過delayer處理的晶片,依然可以先利用絕緣材料將暴露的金屬層隔絕,從而安全地進行FIB加工。

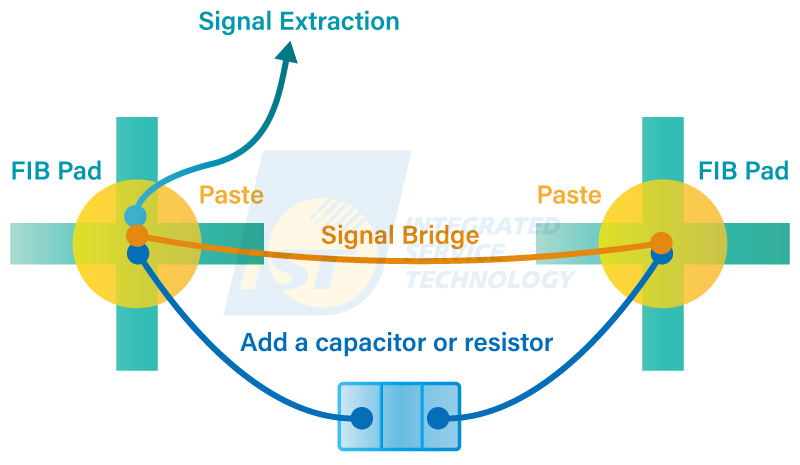

(三)FIB Pad 延伸應用:新型 FIB 電路修補(N-FIB 專利技術)

- 低阻抗解決方案

以1,000um的連接距離為例,使用傳統FIB沉積技術,Pt材質的阻抗為6k Ω,W材質為2k Ω,而N-FIB技術則可實現僅10 Ω的低阻抗,顯著提升效能。 - 訊號引出

取代傳統探針測試,提供更高的靈活性與重複性,應用於更頻繁與複雜的測試需求與環境。 - 添加電容或電阻

利用N-FIB技術連接電容或電阻,使用SMD 0201封裝,尺寸為300*600um,實現更精確的電路測試需求。

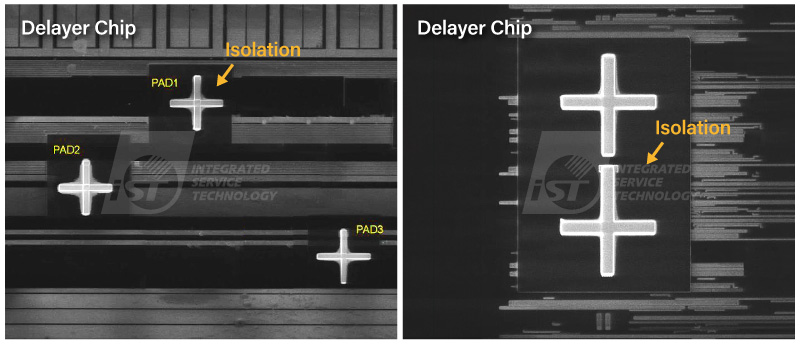

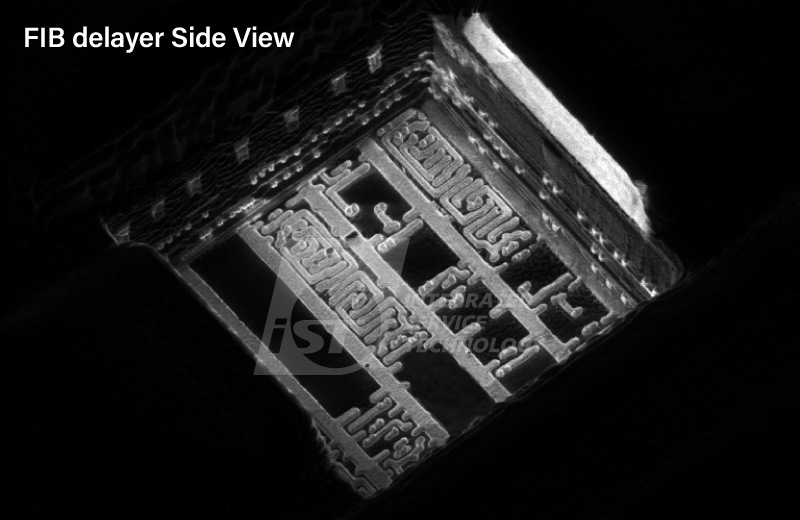

(四)FIB Delayer技術應用於故障分析Nano Probe測試

在測量先進製程或高速訊號功能的晶片時,若使用FIB Pad方式進行測試,可能會因額外增加的阻抗或容抗而導致訊號失真。為了解決這一問題,可以使用宜特故障分析實驗室建置的奈米探針電性量測(Nano Prober)設備,將損耗降至最低。

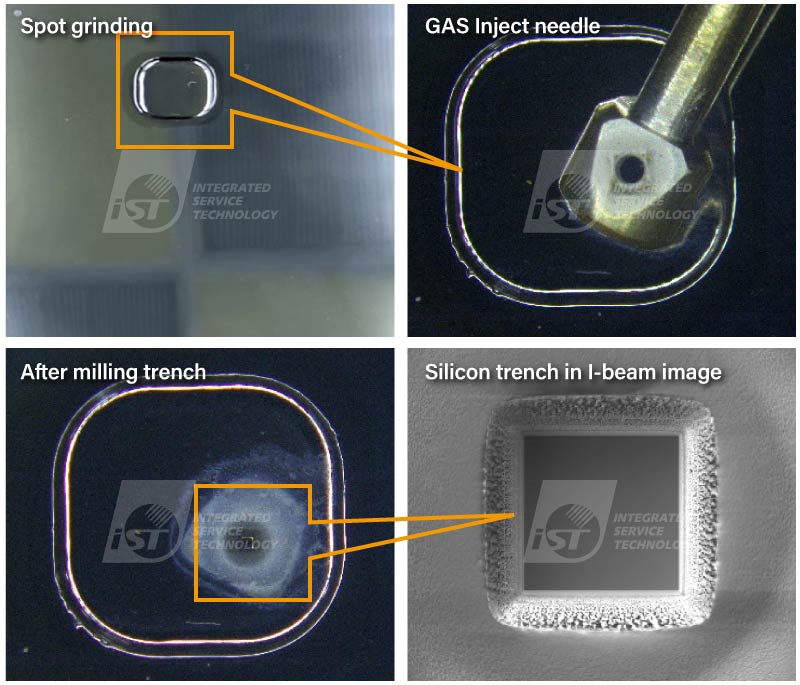

在此之前,須對晶片進行去層(delayer),然而傳統的去層技術需要全面性的逐層研磨至目標金屬層,這不僅耗時,且在面對先進製程晶片時,過度研磨的風險也會相對增加。在這種情況下,FIB可以精確的鎖定局部區域進行去層,大幅降低失敗風險,FIB的蝕刻技術成為一個理想的解決方案。

(五)FIB晶背電路修補技術

晶背電路修補技術是一項經過多年發展且相當穩定的技術,並且已經建立了完整的工作流程,包括開蓋、研磨及重新封裝等,都有對應的解決方案。在這一過程中,特別是針對目標區域進行局部研磨,將能夠實現CoWoS封裝中的FIB電路修補。

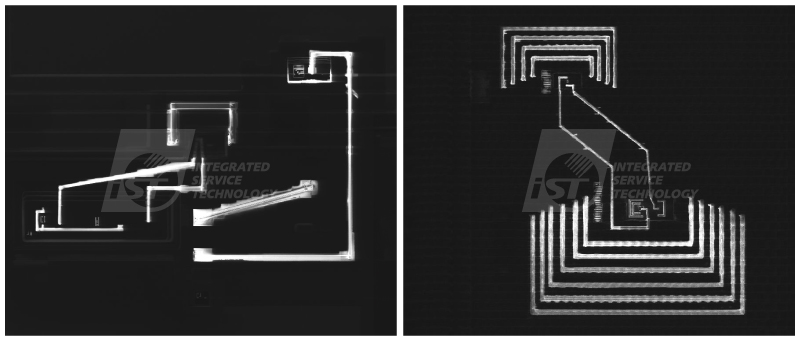

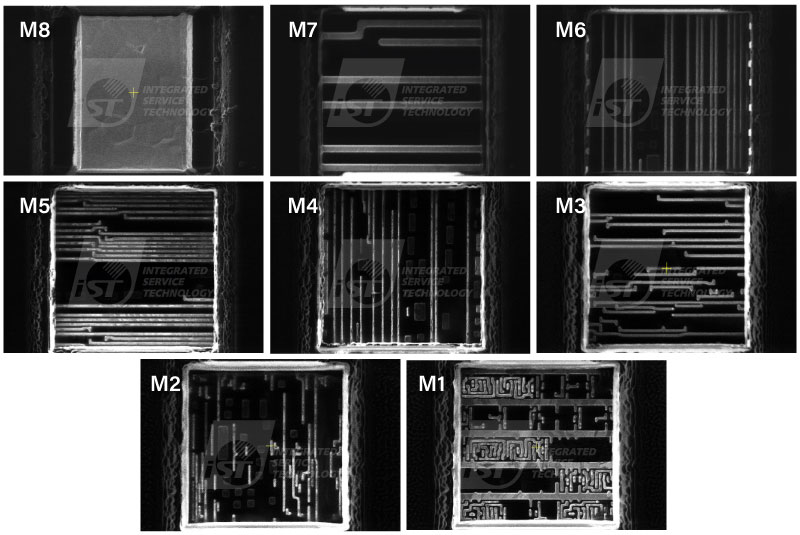

從晶背執行電路修補時,目標通常位在M1~M3的金屬層,都是晶片最小設計尺寸金屬層,往往考驗著實驗室人員的技術能力以及調校出的影像品質。參考圖例展示,宜特利用設備最小beam current 1.2pA 調校高解析度的影像,有助於電路判斷進而提高電路修補成功率。

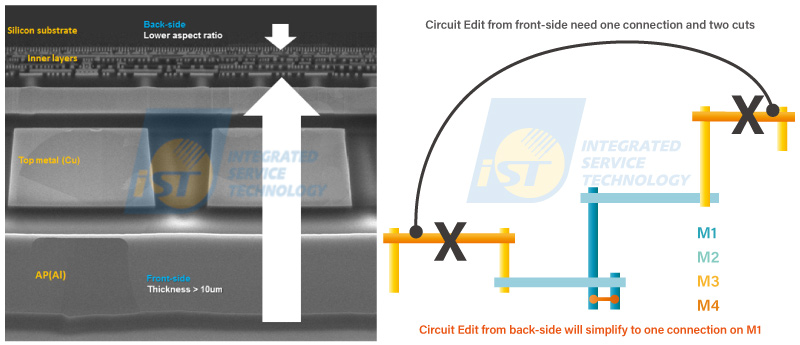

隨著先進製程元件尺寸的持續微縮,以及終端產品需求的不斷推動,Flip Chip封裝的應用範圍逐步擴大,其中CoWoS(Chip-on-Wafer-on-Substrate)封裝也採用了Flip Chip 2.5D封裝形式。從FIB晶背施工的角度來看,Flip Chip封裝具有低深寬比的優勢,並且修改過程會先遇到電路源頭,能夠在一定程度上簡化欲修改的內容。然而,隨著製程節點進入7nm、5nm、3nm,甚至未來的2nm,晶片的電路多樣性與複雜度大幅提升。儘管我們已經展示過成功的3nm修改案例,但這些先進製程所帶來的挑戰,大大提高電路修補的難度。無論是技術能力還是設備能力,都需要具備更高的要求。市場譽為黑科技的晶背供電技術(Backside Power Delivery Network, BSPDN),將成為FIB電路修補技術未來面臨的一大挑戰。

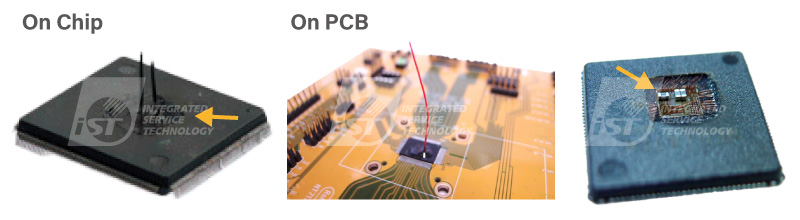

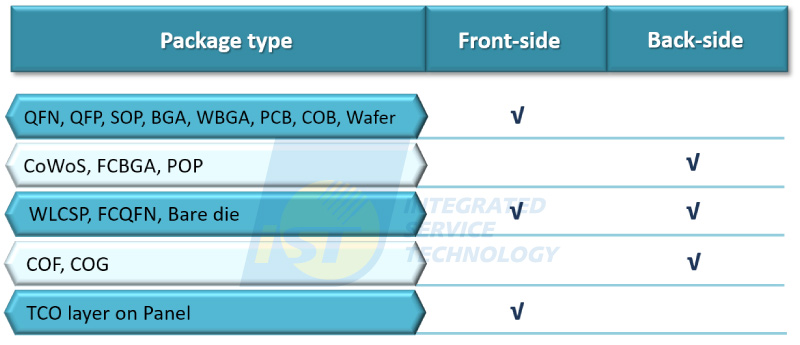

(六)FIB 技術應用於各種封裝

宜特FIB實驗室可滿足市場大部分熱門封裝的FIB電路修補,以下將針對三種特別的封裝,進行解析。

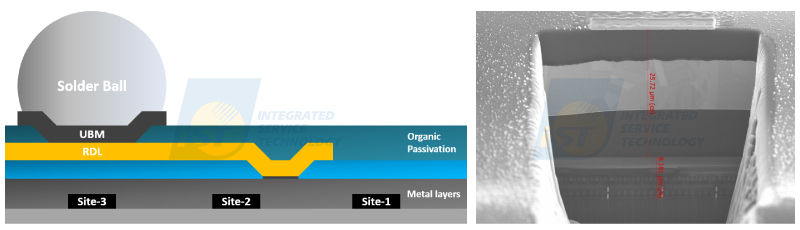

1. WLCSP (Wafer-Level Chip Scale Package)

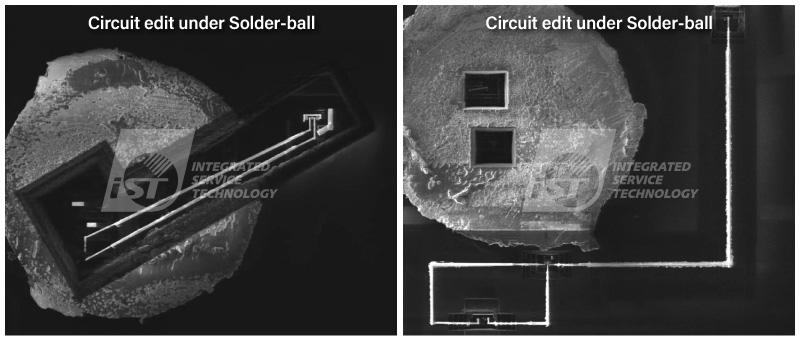

宜特在2014年即提供WLCSP完整的解決方案,除了Site-1、Site-2皆可以執行電路修補外,針對Site-3更提供錫球局部移除與移除重植的方案,解決客戶電路在錫球下無法執行FIB 電路修補的困境,同步提供FIB 晶背電路修補,並成功實現在同一顆樣品上進行晶片正面與背面電路修補的案例。統計自2014年推出後共為全球客戶執行超過10,000顆WLCSP的電路修補。

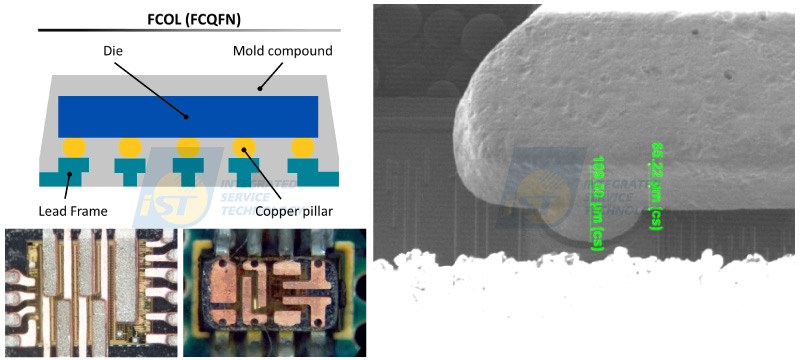

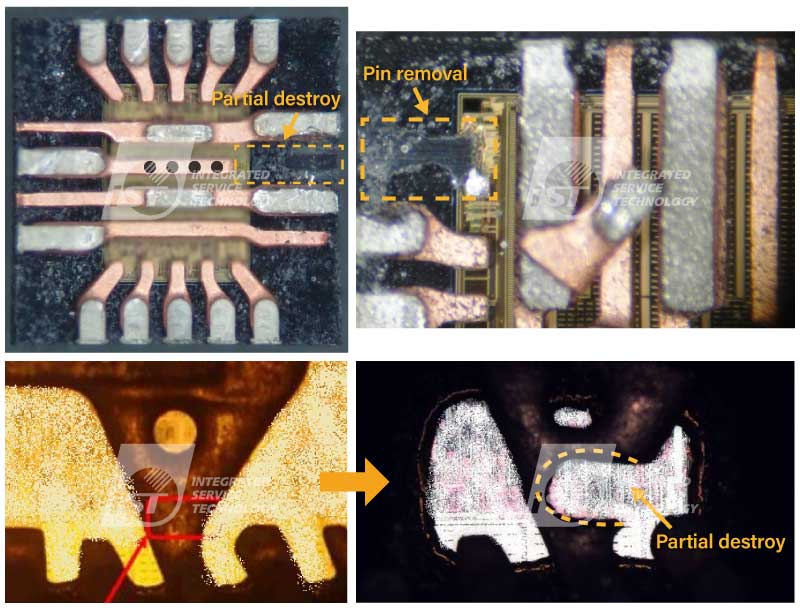

2. FCOL (Flip Chip on Lead)

FCOL封裝技術通過利用銅柱和導線架取代傳統的焊線,不僅縮小了封裝尺寸,同時降低了熱阻與電阻,進而提升了散熱能力與電性效能。然而,晶片上方大面積的導線架卻為FIB電路修補帶來挑戰,當目標區域被導線架覆蓋時,將無法進行FIB修改。為解決這一問題,宜特在2014年提出了局部移除導線架的創新方案,該方法在保持IC正常電性運作的同時,能夠順利完成FIB電路修補,需要注意的是移除封膠體後,裸露的導線架變得相對脆弱,因此在FIB完成後,必須進行封膠處理以增強結構穩定性。此外,必須提醒,一旦導線架被移除,將無法重建,這一點需特別留意。

宜特FIB實驗室,針對FCOL封裝產品,亦同步提供FIB 晶背電路修補,並且成功實現在同一顆樣品上進行正面與晶背電路修補的案例。

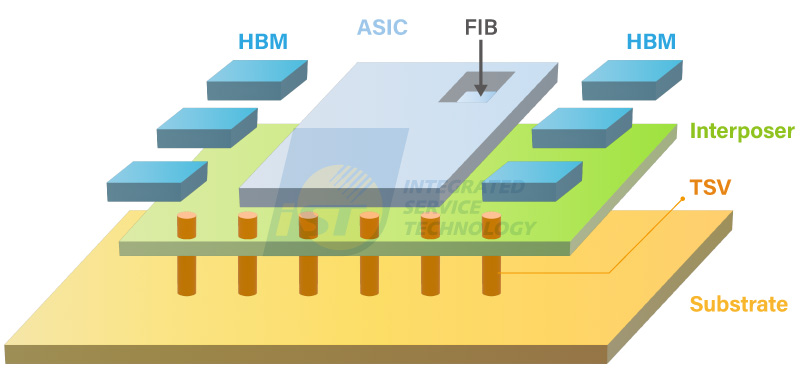

3. CoWoS(Chip-on-Wafer-on-Substrate)

近兩年,CoWoS封裝無疑是最受關注的封裝技術之一,那麼,這種封裝能否進行FIB電路修補呢?答案是肯定的!

從結構示意圖中可以看到,CoWoS採用了2.5D封裝形式,ASIC的正面透過TSV(Through-Silicon Via)連接到基板(Substrate),而ASIC晶片的晶背則為裸露狀態,所以可以從晶背進行FIB電路修補。

然而,在進行FIB修改之前,通常需要先對晶背進行研磨以減少其厚度。傳統上,研磨通常是全面性進行,但這樣容易破壞高頻寬記憶體(HBM)。宜特可以針對FIB的目標區域進行局部研磨,這樣不僅能保護HBM,還能為後續的FIB操作提供必要的空間。

- 低阻抗解決方案

宜特科技是台灣首家執行FIB電路修補的民營實驗室,30年來的電路修補經驗,成功解決了無數客戶的各種挑戰,從簡單的1L1C電路修補到複雜的電路問題;或是從單站的FIB電路修補,到跨越3~4站的故障分析(FA),都能提供對應的解決方案。

2018年,宜特率先提供7nm製程晶片背電路修補服務;2021年初,成功展示了5nm製程的晶片背電路修補技術。2023年底,宜特更成功完成了3nm晶片電路修補案例,幫助客戶迅速確認電路缺陷,降低開發時間與成本,加速產品上市。

宜特FIB電路修補,不僅在各製程節點的技術演進中,始終保持領先地位,成為眾多IC設計公司首選的合作夥伴之外,後續更可結合宜特一站式的故障分析和材料分析解決方案,搭配30年豐富的大數據經驗,將如虎添翼協助IC設計業者解決棘手的晶片除錯問題。本文與各位長久以來支持宜特的您,分享經驗,若您想要更進一步了解細節,歡迎洽詢+886-3-5799909 分機6000 王先生│Email: web_fib@istgroup.com。