發佈日期:2023/10/17薄膜附著力

發佈單位:iST宜特

解決先進封裝技術中不同材料機械特性的問題,奈米壓痕與刮痕測試是關鍵,但究竟該如何搭配SEM&TEM 以找出故障點呢?

薄膜附著力

在半導體積體電路朝向尺寸微小化和功能極大化的發展方向上,先進封裝技術已成為提高晶片性能的重要途徑之一。然而,為了達到垂直整合的目的,多層薄膜堆疊結構已被大量地運用在製程當中。由於不同材料之間的機械特性不匹配,以及製程中產生的熱機械應力,導致的各種失效模式亦接踵而來。為了克服這些瓶頸,對於材料機械特性的掌握變得至關重要,在微米及奈米尺度的世界中,「奈米壓痕測試儀」及「奈米刮痕測試儀」為兩個重要的分析工具。除了可用來分析材料的機械特性,以及多層結構中的附著能力,亦可作為區域化應力的工具,搭配後續影像分析技術,如掃描式電子顯微鏡(SEM)、雙束聚焦離子顯微鏡(DB-FIB)或穿透式電子顯微鏡(TEM)可更進一步地分析內部結構變化,找出造成故障的脆弱點位置。本期宜特小學堂與安東帕公司合作,將針對奈米壓痕及奈米刮痕的測試原理及相關應用進行說明。

薄膜附著力

薄膜附著力

一、奈米壓痕和刮痕測試儀的原理

奈米壓痕測試法及刮痕測試法,為兩種廣泛用於研究材料微機械特性的技術。利用此二種方法,可助於了解材料於微米及奈米尺度下,因應力所產生變形或破壞的機制,與傳統測試方法(如維氏或洛氏硬度等)相比,能夠提供更多特徵參數而非僅僅單一硬度值(延伸閱讀: 異質整合當道 材料接合應力強度備受矚目)。

奈米壓痕測試儀,具有精密的應力和深度感測器,可精準控制壓頭進行載入與卸載過程,並同時記錄載荷及壓入深度,進而得到與壓痕深度相關的各項材料參數,如代表材料抵抗永久變形能力的「壓痕硬度 (Hardness,簡稱HIT)」、用來描述材料彈性的「彈性模量 (Elastic modulus,簡稱EIT) 」以及材料於固定荷載下持續變形的行為「蠕變特性(Creep,簡稱CIT) 」等。

而刮痕試驗儀,則用來測量薄膜與基材間或是薄膜本身的結合力,藉由逐漸線性地增加施加於鑽石刮頭上的力量,於材料表面上產生出剪切力。當薄膜與基材本身的機械性質不同時,在臨界負載(Critical Load, Lc)下會產生附著破壞。此臨界負載為一項良好的量化參數,可用來代表薄膜的附著能力。在同一刮痕過程中,擁有較大的臨界負載的材料具有較佳的附著能力,能夠更好地抵抗後續製程中的熱應力衝擊。

二、奈米壓痕和刮痕測試儀的四大應用

(一)利用奈米刮痕探討多層膜的脫層現象

為了實現3D IC封裝技術,半導體元件的結構朝向高度多層化發展-將各種具有不同特性的薄膜材料堆疊在一起。然而,當多層結構在受到不同製程中帶來的熱及機械應力後,因薄膜/薄膜或是基材/薄膜間機械特性不匹配(如熱膨脹係數、楊氏模數或蒲松氏比等)而導致『界面剝離 (interfacial delamination)』現象的發生不斷地出現於製程當中,為目前常見導致元件失效的原因之一。

為了改善此問題,掌握材料間的附著能力,以及了解結構在外部應力下的行為變得至關重要。奈米刮痕測試儀是一個很理想的分析方式,除了可用來量化界面剝離作用力,亦可施加外部應力,模擬材料因外部應力而失效的過程。此外,於界面剝離發生後,結合掃描式電子顯微鏡(SEM)、雙束聚焦離子顯微鏡(DB-FIB)或穿透式電子顯微鏡(TEM)可更進一步地分析多層內部結構變化,找出結構中的脆弱處。

以圖二Si/SiO2(SiN)/TiN/W多層結構為例[1],利用直徑為2 微米的鑽石刮頭,以 2 mN/s的正向力加載速度,分別於兩個不同多層結構樣品表面創造出刮痕(如圖二)。由刮痕測試儀分析數據可知,樣品A及樣品B的臨界負載分別為 7 mN及 15 mN。代表樣品 B具有較佳的抗外應力能力。此外,結合穿透式電子顯微鏡(TEM)及X射線能譜 (EDS)的成份分布(mapping)分析顯示,此二結構發生界面剝離的位置位於 SiO2/TiN 及SiN/TiN界面。

(二)銅柱凸塊 (Cu pillar bump)的機械特性分析

為了滿足終端產品輕薄短小的需求,晶片訊號處理輸入輸出需求數量不斷增加,這意味著晶片封裝中的引線節點數密度需要提高,而用於連結積體電路晶片與基板的凸塊 (Bump)間距則需不斷縮小。銅材料因具備良好的低電阻、低電感、低熱阻,以及抗電子遷移能力等特性,銅柱凸塊(Cu Pillar Bump)成為實現小間距的優異選擇。薄膜附著力

然而,當凸塊間距縮小至10微米左右時,許多的問題相繼出現[2]。舉例而言,銅柱凸塊結構在經過迴焊製程(Reflow Process),因熱應力而導致「橋接失效(Bridge Failure)」現象為一待克服的議題。

為了解決這些問題,我們可以使用搭載顯微鏡頭的奈米壓痕測試儀,於特定的銅柱位置進行壓痕實驗,已獲得不同區域的機械特性分析,從而優化製程參數。圖三為利用高速電鍍方式製備的銅柱凸塊[3],搭配不同的製程方式以及奈米壓痕實驗,可掌握電鍍製程中電通量對於銅柱機械特性的影響。由圖三(b)可知,銅柱的硬度與電鍍製程中施加的電通量呈現正相關。

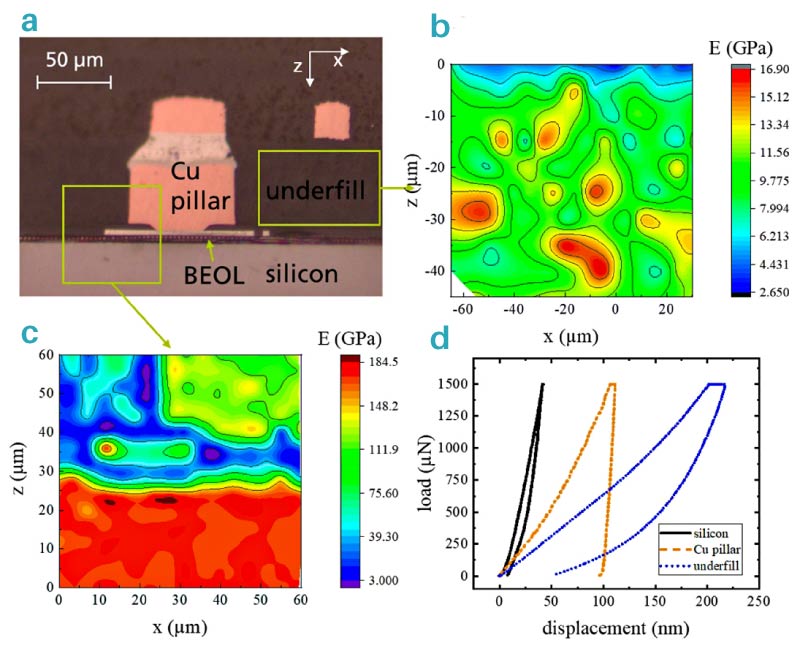

(三)底部填充材與凸塊間機械特性匹配的分析

於IC覆晶(Flip Chip)封裝製程中,會於凸塊間填入底部填充材料(Underfill)來強化晶片的機械穩定性及提高整體可靠性。Underfill主要為高分子材料,其楊氏模量及熱膨脹係數,與周圍的銅柱凸塊以及底下的矽基材[4]存在顯著差異,由於機械特性的不匹配,晶片在後續高溫高濕可靠度的測試中,可能出現各種故障模式,例如裂紋產生、基板分離、空洞(閱讀更多:如何利用真空壓力烤箱 消滅Underfill Void)等。

為了找出這些故障的主要原因,解析結構中不同位置機械特性的差異就顯得尤其重要。近年來,奈米壓痕測試儀已廣泛地被用來量測結構中不同位置的機械特性。圖四(a)為填充完underfill結構的剖面圖,利用奈米壓痕搭載的光學顯微鏡可選定三個不同的區域進行分析,此三個區域包含了銅柱凸塊、底部填充材、後段製程晶片以及矽晶片。

由圖四(b)結果可知,楊氏模量的不均勻分布顯示underfill中還存在其他填充物。圖四(c)則可以看到銅柱凸塊與晶片間界面的彈性模量分布。於特定位置進行壓痕測試分析,可得到矽晶圓、銅柱凸塊以及underfill的楊氏模量。如圖四(d)顯示,其分別為169 ± 3 GPa, 119±6 GPa and 9 ± 3 GPa。[4]由此結果可發現,由於模量的顯著差異,增加了此結構因後續製程產生的失效風險。薄膜附著力

因此搭配壓痕測試儀的結果,可有效尋找較適化的製程參數,或透過更改不同特性的材料,來避免因機械特性不匹配造成產品的故障。

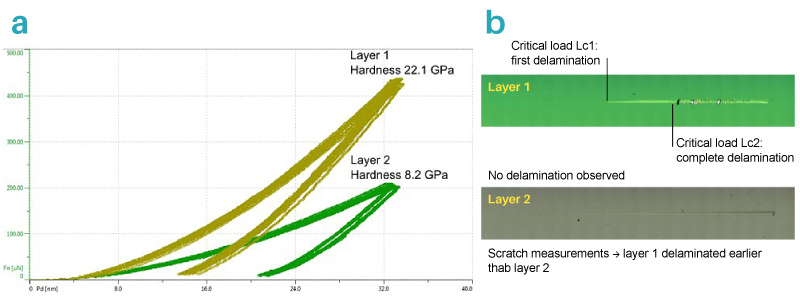

(四)鈍化保護層硬度與附著能力相關性的分析

在晶圓級尺寸封裝(Wafer Level Package)結構中,為了於基板上製作出如電晶體的主動裝置,利用各種不同的沉積方法於底材上方堆疊出金屬層、包含線路重佈的金屬線層(RDL)、用以連接電路的金屬墊(Pad)以及鈍化保護層(Passivation layers)。[5] 鈍化保護層的主要作用是保護底下結構不致受到外在環境的污染或損傷。不同的沉積方式或製程條件,對於鈍化保護層的機械特性及與底材的附著能力有顯著的影響。結合奈米壓痕測試儀及刮痕測試儀量測結果,不僅能夠找出薄膜機械特性及附著能力的關係,亦可加速製程優化及保護層材料的篩選,從而加快後續的開發流程。

以氮化矽(SiNx)薄膜為例,圖五(a)為利用兩種不同製程方式於矽晶圓表面沉積出厚度約為300 奈米薄膜的載荷-壓深曲線。由結果可知,Layer 1的硬度高於Layer 2。而進一步地利用刮痕測試儀分析其附著能力時卻發現,Layer 1在較小的載荷下就觀察到界面剝離現象,相反地,於同一刮程下,Layer 2並未觀察到界面剝離現象 ,此結果表示Layer 2的附著能力大於Layer 1。薄膜附著力

若比較壓痕測試出來的結果,可有趣地發現,雖然Layer 1擁有較高的硬度,但附著能力並未較佳。由此結果可知,薄膜的機械特性和附著能力的展現並非都呈現正相關性,因此須結合二者全方面的探討才能找出最適化的材料特性。

近年來,隨著封裝技術不斷的演進,傳統單一的大面積素材已不符合3D複雜結構的應用,微小空間中不同尺寸晶片的結合、並列或堆疊的趨勢則日益明顯,但如此微小結構中的異質材料,在封裝後受到機械應力互相影響的因子也變得更加複雜,因此,除了必須具備精密的微區機械特性量測能力之外,結合影像判斷的SEM、DB-FIB及TEM電子顯微鏡也成為必要的分析工具。在未來IC的先進封裝技術開發中,宜特科技將持續不斷地與所有合作的客戶共同努力,研發出更有效率的下一代晶片,使得我們未來生活更多采多姿。

本文與長久以來支持宜特的您分享。若您有相關需求,或是對相關知識想要更進一步了解細節,歡迎洽詢 +886-3-579-9909 分機 6176 江先生 / Email:web_sa@istgroup.com;marketing_tw@istgroup.com。

參考文獻:

[1] Jin-Hoom Kim, Hye-Jun Kil, Sangjun Lee, Jinwoo Park, and Jin-Woo Park. ACS Omega 2022, 7, 25219−25228.

[2] https://technews.tw/2022/07/29/ma-tek-package-design-hybrid-bonding/

[3] Pei-Tzu Lee, Chih-Hao Chang, Cheng-Yu Lee et al. Materials & Design 206 (2021) 109830 “High-speed electrodeposition for Cu pillar fabrication and Cu pillar adhesion to an Ajinomoto build-up film (ABF)”

[4] Thesis with the title “Micromechanical indentation study of stress related effects in transistor channels” by Simon Schlipf

[5] 中華民國專利,申請案號:102121292

![圖以Si/SiO2(SiN)/TiN/W多層結構為例[1],利用直徑為2 微米的鑽石刮頭,以 2 mN/s的正向力加載速度,分別於兩個不同多層結構樣品表面創造出刮痕](https://www.istgroup.com/tw/wp-content/uploads/2023/10/tech_20231017-02-Thin-film-adhesion-hardness-1.jpg)

![薄膜附著力 圖三:(a) 不同電通量電鍍製程產生銅柱的SEM影像。 (b)銅柱硬度、彈性模數與電鍍電通量關係圖。[3]](https://www.istgroup.com/tw/wp-content/uploads/2023/10/tech_20231017-03-Thin-film-adhesion-hardness-1.jpg)