發佈日期:2021/4/7IC快速封裝

發佈單位:iST宜特

近期封裝廠產能爆滿,無法支援IC研發設計階段所需的少量封裝工程樣品,拖累新產品開發時程,如何解?

IC快速封裝

2020 COVID-19疫情爆發後,傳統封裝訂單大爆發,如遠距商機(WFH)等帶動的PC/NB週邊晶片需求、消費電子晶片需求,及車用電子力求穩定度的QFN封裝等,帶動打線封裝產能滿載。

而傳統大型封測廠2021年第一季接單明顯爆滿,甚至在2021年上半年訂單能見度都是一路暢旺,在封測產能沒有大舉擴充的跡象下,已成為IC設計出貨卡關的瓶頸,更遑論研發設計階段所需的工程樣品,更是拿不到封裝廠的資源。

一般而言,IC設計公司在研發階段,取得試產品-晶圓/晶片後,必須過封裝製程,才能進行後續的工程驗證。

然而,近期宜特科技就觀察到,越來越多客戶在來宜特進行工程驗證時,會先尋求宜特協助進行工程樣品快速封裝; 最大原因就在於大型封裝廠處理量產品已應接不暇,IC設計客戶既定要驗證的小量生產的一次性工程(NRE, Non-Recurring Engineering)封裝需求,不斷地被延宕交期,因此找上宜特尋求協助。

宜特快速封裝實驗室,已成立20多年,每年替客戶完成數十萬顆實驗性工程樣品的 IC快速封裝 打線。本期宜特小學堂,將帶您一窺,宜特快速封裝實驗室,實際上是如何運作讓您可以在短短數小時內,就拿到封裝樣品;而針對特殊晶片封裝樣品的測試瓶頸,宜特是如何提供解決方案,協助您後續量測無礙。

一、正常晶片封裝樣品: 透過陶瓷等材料,六小時完成工程樣品快速封裝

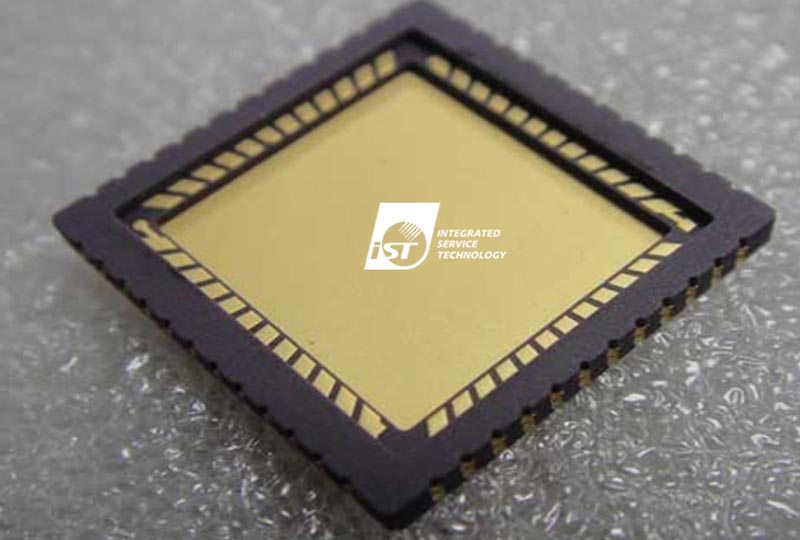

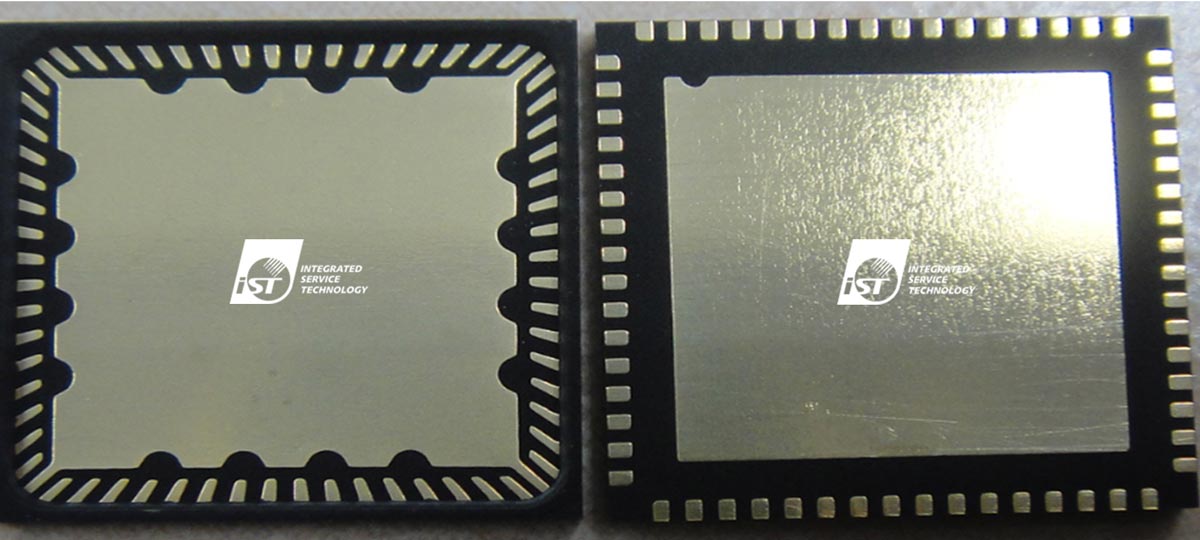

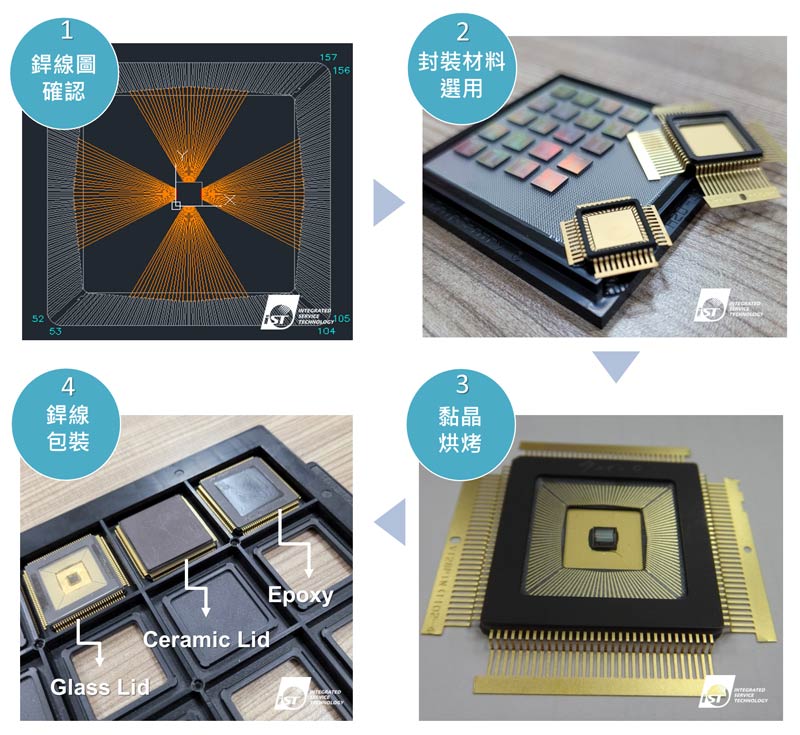

傳統量產品的封裝多使用導線架(Leadframe)與載板(substrate),封裝製程多達20-30道,交期從3到10天不等。而針對實驗性的工程樣品,宜特快速封裝實驗室則是透過陶瓷(參見圖一)、塑膠預成型(plastic pre-mold)(參見圖二)等材料,與公版PCB製作,精簡製程只需4道(參見圖三)。

首先,封裝焊線圖確認,您可以提供封裝廠的銲線圖,或是將晶片資料提供給宜特,宜特將選用適當規格材料後,繪製出封裝焊線面圖,確認無誤即可進行正式樣品作業。接著,依據客戶需求,使用導電或非導電膠,黏貼晶片在封裝材料上,再依照晶片規格,選用適當線材、線徑進行銲線作業。

最後因應客戶測試或使用方式,宜特可提供玻璃蓋、陶瓷蓋或是使用封膠方式保護晶片與銲線,即可縮短交期最快6小時即可取得封裝樣品,供後續工程驗證使用。

二、特殊晶片封裝樣品: 非正常量測需求,如何進行電特性量測?

IC設計工程師會將封裝後的樣品回自家廠內進行電性量測確認設計是否有異常,但如果需要量測特殊訊號,卻無法透過原封裝取得資料,像這種特殊的封裝案例,如何解呢?

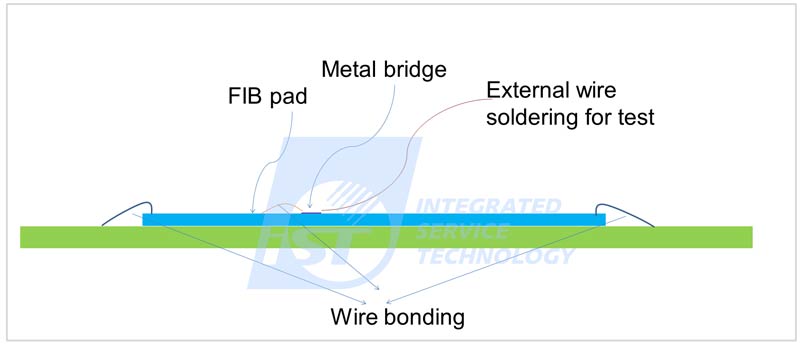

案例一: 使用新型FIB電路修改顯微鏡(N-FIB),亦即在晶片表面使用聚焦離子束形成導電孔及銲墊,再利用特殊接合方式使銲墊連接金屬橋梁,藉以形成導線路徑(參見圖四),使客戶能進行後續量測作業。

圖四: 透過宜特新型 FIB 電路修補 (N-FIB),形成導線路徑

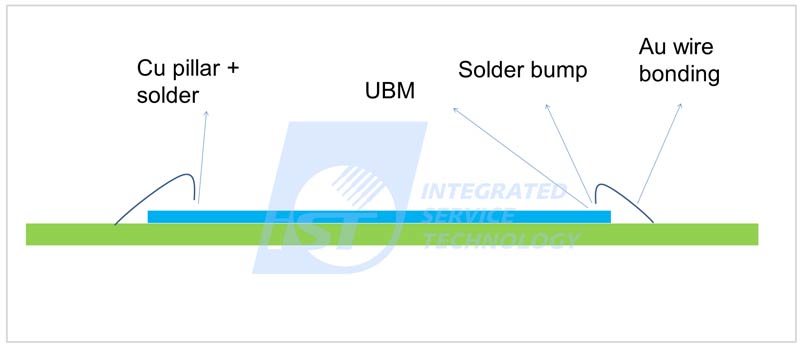

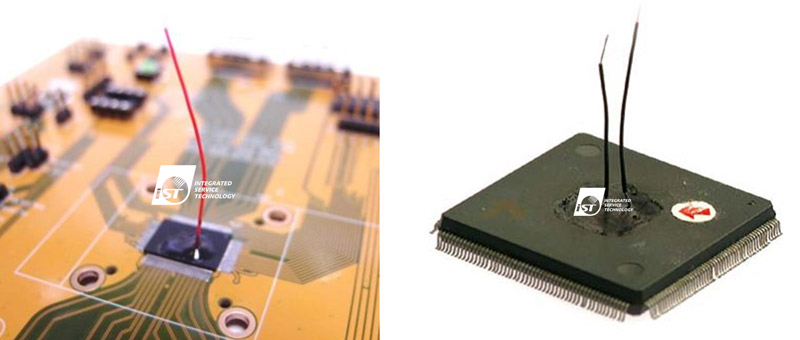

案例二:客戶提供非銲線封裝型態晶片需要進行驗證,無論是錫球或銅柱,透過特殊的銲線參數,宜特可以快速進行銲線,協助客戶進行後續實驗(圖五)。

圖五: 宜特快速封裝實驗室由特殊的焊線參數,可將晶片(Die)上的訊號以金屬線引出,供工程師進行後續量測。

圖六:訊號引出實例圖

本文與各位長久以來支持宜特的您,分享經驗,除了快速封裝外,宜特實驗室也可提供樣品晶圓切割(wafer saw)、高精度多功能黏晶(die attach)與IC打線/封裝(wire bond)等服務,也可配合您的晶片與客製化基板提供先進覆晶(flip chip)封裝服務,以利後續您進行ESD、OLT、可靠度等分析驗證一站式(One-stop Solution)的高品質服務,有效縮短測試樣品的製作時間。若您有相關需求,或是對相關知識想要更進一步了解細節,不要猶豫,歡迎洽03-579-9909分機6861陳先生(Peter)│ Email: ist_assy@istgroup.com。