發佈日期:2020/10/22覆晶封裝

發佈單位:iST宜特

晶片若只有打線鋁墊(Al Pad) ,如何進行覆晶黏晶鍵合(Flip Chip Die Bonding)?

先進封裝時代,銅柱凸塊逐漸取代錫凸塊,特性不同,如何避免空焊或位移?

覆晶封裝

黏晶製程(Die Bonding)雖然只是半導體後段封裝眾多製程中的一項製程,然而隨著終端產品輕薄短小及5G時代的來臨,封裝也朝向微小化、立體化發展。那麼如何縮小尺寸,同時又能維持其特性成為重要課題。

黏晶技術最困難在於如何用各種黏晶鍵合技術(Die Bonding)及最少的介質,將晶粒精準固定在基板或是將晶粒堆疊到最薄,並且可以達到電性不失真及通過各項可靠度測試。

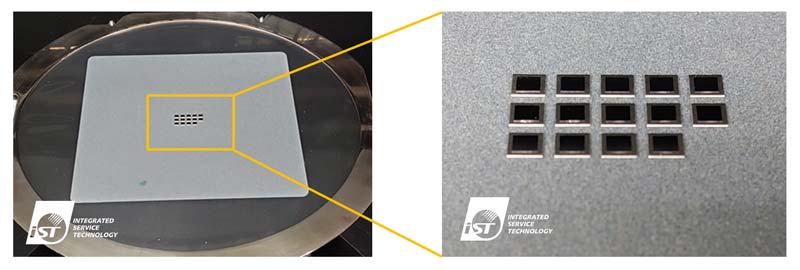

以往黏晶鍵合(Die Bonding)都以人工作業為主,不過身為半導體驗證分析的宜特科技,為了協助客戶在研發製程階段,可以順利進行各項驗證測試與實驗分析,因此在去年引進自動化黏晶(Die Bonding)設備,解決了許多人工作業無法達到的黏晶品質(閱讀更多: 自動化Die Bonding 黏晶技術, 工程樣品快速封裝無礙 )

本期小學堂,宜特將分享幾種常見的黏晶鍵合技術案例。

一、晶片只有打線鋁墊(Al Pad),如何進行覆晶黏晶鍵合(Flip Chip Die Bond)

覆晶(Flip Chip,簡稱FC)封裝在晶圓製程最後階段,通常都會遇到球下金屬層(Under Bump Metallurgy,簡稱UBM)或重分佈製程(Redistribution Layer,簡稱RDL)。

不過,有一種情況是,IC在設計研發階段時,為節省成本,以晶圓共乘(CyberShuttle) 下線後,卻發現自家晶片回來後沒有UBM層或RDL層而無法長錫球, 導致後續無法進行驗證覆晶封裝的電性狀況。

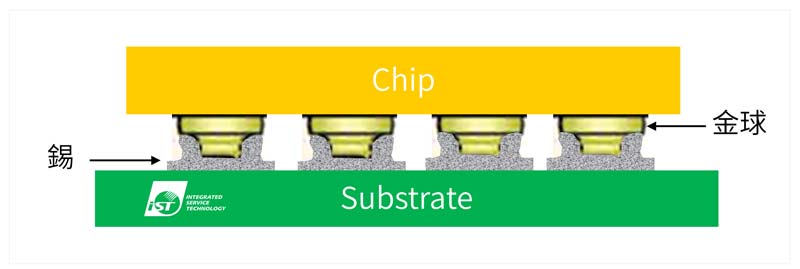

如何解決此問題? 宜特快速封裝實驗室,透過在鋁墊(AI Pad)上長出金球,再焊接到基板(Substrate)上,達到晶片上只有鋁墊也可以進行打線(Wire Bond,簡稱W/B)封裝驗證或覆晶(Flip Chip,簡稱FC)封裝驗證 (參見圖一) 。

圖一: 宜特透過鋁墊長出金球,焊接至基板結構圖

二、小間距的覆晶封裝,從傳統的錫凸塊逐漸被銅柱凸塊取代,如何避免空焊或位移?

隨著封裝尺寸縮小,覆晶(Flip chip,簡稱FC)封裝貼合時需要更高的對位精準度,接合凸塊(Bump)也從早期廣泛使用的錫凸塊(Solder Ball)或稱為錫球(Solder Ball),發展到現今小於150um小間距的銅柱凸塊(Copper Pillar Bump)。

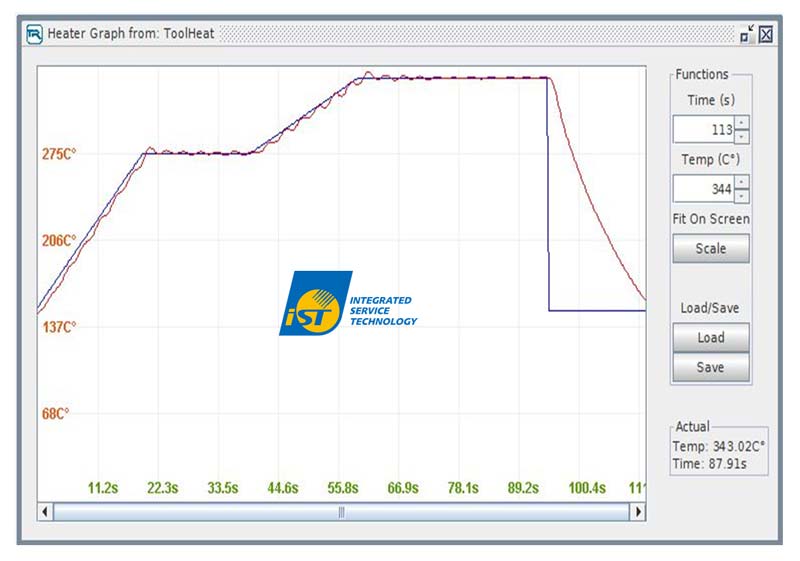

然而,隨著覆晶封裝接合凸塊材料的多樣性,焊接時溫度曲線控制也變得更複雜(參見圖二)。

圖二:隨著覆晶封裝結合凸塊材料的多樣性,在貼合時除了需要更精準的對位系統,銲接時的溫度曲線(Temperature profile)誤差範圍也較小

不同於傳統的錫球(Solder Ball)只能提供機械性、電性和被動式的散熱功能;銅柱凸塊(Copper Pillar Bump)具有良好的散熱、導電特性,亦具有低電阻、低電感、低熱阻特性,以及較佳的抗電子遷移能力,以及較微小的凸塊接點間距,滿足近年來終端產品輕薄短小的需求。

由於這些特性將增加訊號傳遞能力和可靠度,因此使用銅凸塊(Copper Pillar Bump)能開發出更複雜的封裝IC,例如3D IC,藉此朝功能更強大、且更微小精密的系統整合發展。

然而,銅柱凸塊(Copper Pillar Bump)間距多數小於150微米(um),不像錫球(Solder Ball)焊接點大,能容許較大的偏移與溫度曲線範圍,在樣品製備時期,只要使用熱風槍或加熱盤進行加熱,即可將樣品上到基板。

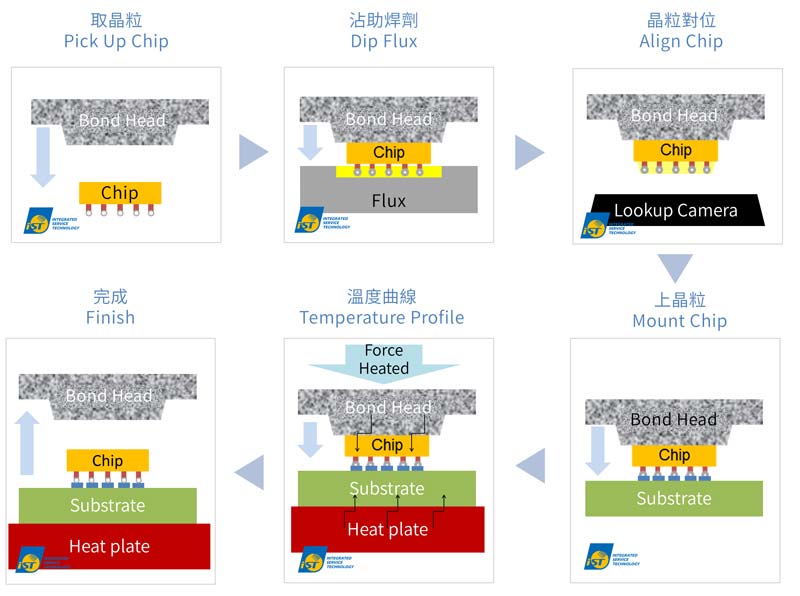

銅柱凸塊(Copper Pillar Bump)上的錫厚度只有20-50微米(um),使用熱風槍或加熱盤加熱,極容易造成空焊或位移;因此,在鍵合時,就需要有更精密的對位系統,焊接時的溫度曲線範圍也較小。然而,研發階段這種少量多樣的銅柱凸塊覆晶黏晶鍵合(Copper Pillar Flip Chip Die Bond),多數大型封裝廠不願意協助進行,宜特為協助客戶在研發階段順利進行樣品製備,也特別開發銅柱凸塊(Copper Pillar Bump)黏晶鍵合少量多樣服務,作業流程參見圖三。

圖三:銅柱凸塊黏晶鍵合(Copper Pillar Die Bond) 流程

三、如何進行共金黏晶(Eutectic Die Bond)?

共金黏晶也稱為共金貼片(Eutectic Die Attach),應用在需要高散熱、高可靠度封裝黏晶製程上,例如高功率放大器、高功率LED等。

不同於一般使用接著劑黏晶,數量少的工程樣品可以使用人工黏晶作業,共晶黏晶過程中需要使用溫度曲線及壓力,使二種不同金屬鍵合,此部分需要有自動化設備搭配相關流程即可完成。以下分享兩種常見案例:

(一) 使用預成型焊錫片(Solder Preform)黏晶(Die Bonding)

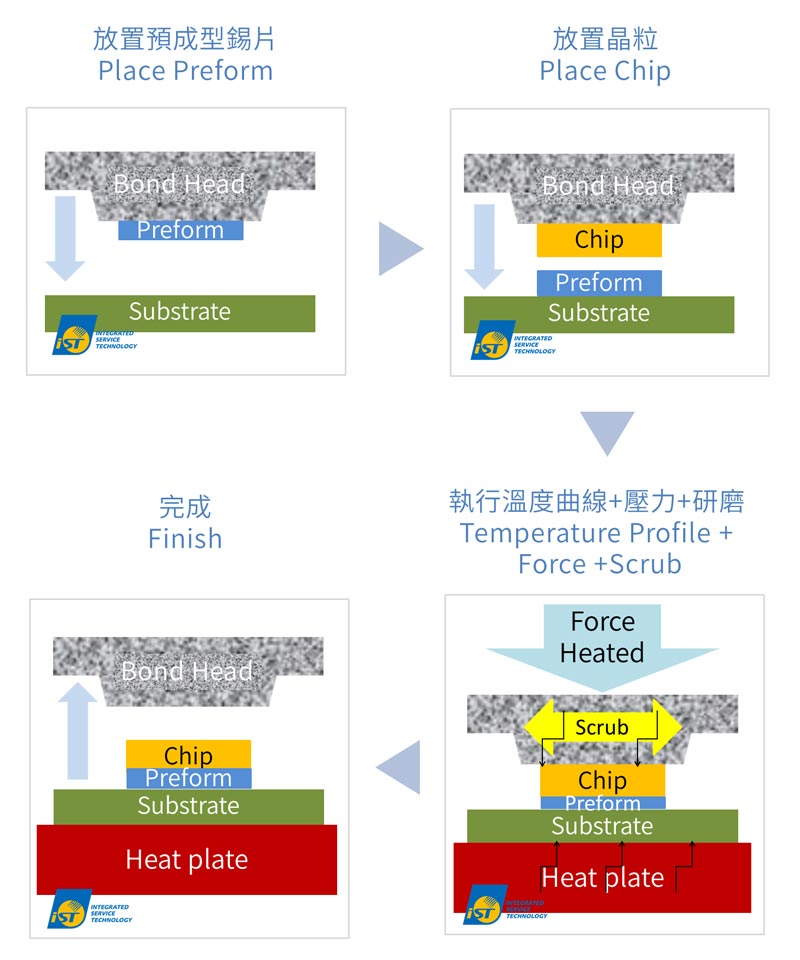

「預成型焊錫片」是將焊錫預先加工成需要的形狀尺寸。使用預成型銲錫片黏晶,需要搭配溫度曲線及壓力方能完成黏晶,但是在黏晶過程中,晶粒與基板(Substrate)間,容易因為銲錫片或基板不平整而產生間隙,造成可靠度疑慮。宜特快速封裝實驗室,建議使用 「擦洗(Scrubbing)技術」,即可將銲料產生的間隙去除,作業流程參見圖四。

圖四: 預成型焊錫片黏晶(Solder Preform Die Bonding)流程

(二) 晶粒倒裝後,銲墊(Pad)直接結合在基板(Substrate)上

若晶粒銲墊(Pad)的表面材質為金,一般金對鎳金結合會使用熱壓超音波(Thermosonic)製程,目的為降低作業溫度,避免作業高溫使金屬表面生成氧化物造成共金不良。 宜特快速封裝實驗室在加熱區加入惰性氣體-氮氣,使用熱壓(Thermocompression)製程溫度,可減緩高溫金屬氧化速度,並搭配溫度曲線及壓力等獨家參數,克服高溫氧化問題,後續亦可串接宜特故障分析和可靠度驗證實驗室,透過X光線(X-ray)或推拉力實驗(Die Shear)確認焊接品質。作業流程參見圖五。

圖五: 金-鎳金 (Au- NiAu) 黏晶流程

四、如何順利將晶粒挑撿到晶圓環(Die Sorting to Wafer Frame)?

本文與各位長久以來支持宜特的您,分享經驗,除了黏晶技術問題,若您有工程樣品封裝、客製化封裝需求,或是對相關知識想要更進一步了解細節,不要猶豫,歡迎洽+886-3-579-9909分機6862楊先生(Benson)│ Email: ist_assy@istgroup.com。