發佈日期:2020/3/26晶片去層

發佈單位:iST宜特

你或許知道可以利用逆向工程了解IC設計架構,避免專利糾紛。

然而利用晶片去層完整提取電路,是有技術性難度的,該如何克服?

晶片去層

隨著摩爾定律,製程演進至7奈米、5奈米甚至達3奈米,晶片裏頭的die,幾乎是接近螞蟻眼睛大小,一般人眼無法辨識。因此,希望藉由一般的 晶片去層 (delayer)來完整提取die裏頭每一層的電路,難度是非常高,硬是下去進行一般層次去除(delayer)技術的後果,不只是良率偏低,更可能發生連die都去除到不見遺失的窘境。

但,為了做專利迴避、或是需完整呈現該層電路圖找Defect時,還有什麼方式可以完整提出電路圖呢?

逆向工程,又稱反向還原工程(Reverse Engineering),不熟悉此工程的人,常常將之與駭客、盜版、竊盜連結在一起。但其實不盡然,隨著專利戰盛行,逆向工程對於許多企業而言,不僅是用來保護自身的專利,確保競爭對手不能非法使用這些專利,同時也保護自己不會侵犯到競爭對手的專利。

而對於半導體產業而言,逆向工程更一直是IC研發設計的主軸,可以協助IC設計公司在開發新產品所需的成本、工時、人力與技術作全面性的分析,並在電路提取上可針對有專利性的電路,經專利地圖資料庫分析比較以做好專利迴避,藉此了解市場態勢並掌握商機。

以往一般的取Die後去層(Delayer)的技術,會因為樣品過小等因素,導致die不見或crack而無法進行製程分析;當無法去層(Delayer)到金屬層(Metal) M1時,記憶體(memory block)僅能以推測得知,電路模組分析圖亦無法完整繪製。

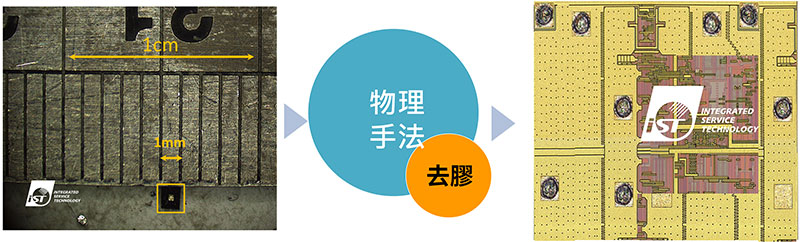

本次小學堂,將與長久以來支持宜特的您,分享宜特如何利用獨家晶片去層技術,將樣品如魔術般放大,直接在晶片封裝(Package)還存在的情況下進行去層工程,不僅可以大幅提升工程上的良率,完整提出電路圖,還可衍生應用在合金PAD、精密IC及其他無法取Die卻需要去層的晶片樣品上。

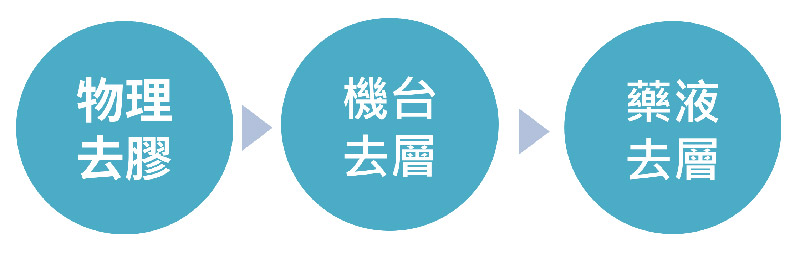

三步驟, 晶片去層 ,避免Die損壞,完整提出電路圖

圖一:宜特獨家開發晶片去層手法,完整提出電路圖

第一步驟 : 樣品製備-物理方式去膠體

第二步驟 : 機台去層

第三步驟 : 藥液去層

本文與長久以來支持宜特的您,分享經驗,若您有任何晶片去層(delayer)需求,或是對相關知識想要更進一步了解細節,歡迎洽詢+886-3-579-9909 分機6739蘇先生│Email: ca@istgroup.com