發佈日期:2019/3/14

發佈單位:iST宜特

隨著製程越微縮,越小製程的晶片,該如何成功完成FIB電路修補?

隨著摩爾定律,半導體製程從1微米(um)、0.5微米(um)、0.13微米(um)不斷微縮到奈米(nm)等級,如此先進製程的電路修補,考驗FIB實驗室的技術發展及應用能力。特別當製程來到16奈米(nm)以下的製程,包裝型式多數為覆晶技術(Flip Chip),因此FIB電路修補就必須從晶片背面(簡稱晶背,Backside)來執行,整體困難度也隨之增加。

2018年,宜特IC FIB電路修補實驗室,就陸續收到7奈米(nm)製程,必須從晶背進行電路修補的樣品。據了解,此樣品難度之高,令其他同業望IC興嘆、束手無策。宜特早年是從IC FIB電路修補起家,2015年時完成20/16奈米(nm)晶片正面的電路修補技術,並於2016年挑戰完成16奈米的IC晶背(Backside)FIB電路修補技術(參見圖一)。近期宜特接到7奈米(nm)的案子,藉由多年經驗,成功完成此電路修補。

本次小學堂,將與各位聊聊,先進製程等級及 7奈米IC晶背電路修補的難度,以及宜特如何克服完成它。

一、 7奈米線路微縮倍增,難度大提升

能夠讓您的IC樣品在FIB電路修補後,可以回去做電性測試,是不論怎麼樣的製程都必須要的基礎條件。有了這個前提下,宜特工程師將會和您討論三大要點:

- 瞭解您設計的IC電路特性與修補目的

- 建議電路布局及討論可破壞範圍

- 精準協助您尋找最佳目標點,提高電路修補可行性。

而當隨著晶片電晶體的密度隨著製程微縮而倍增,今年7奈米每平方毫米的密度約為16nm的3.5倍,難度肯定大幅度上升。不過不管什麼製程,以上三大要點是FIB電路修補前需討論溝通的基礎工,怠忽不得。

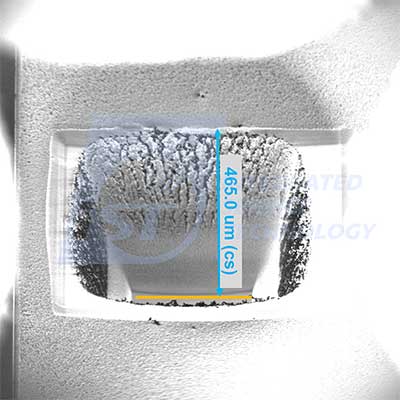

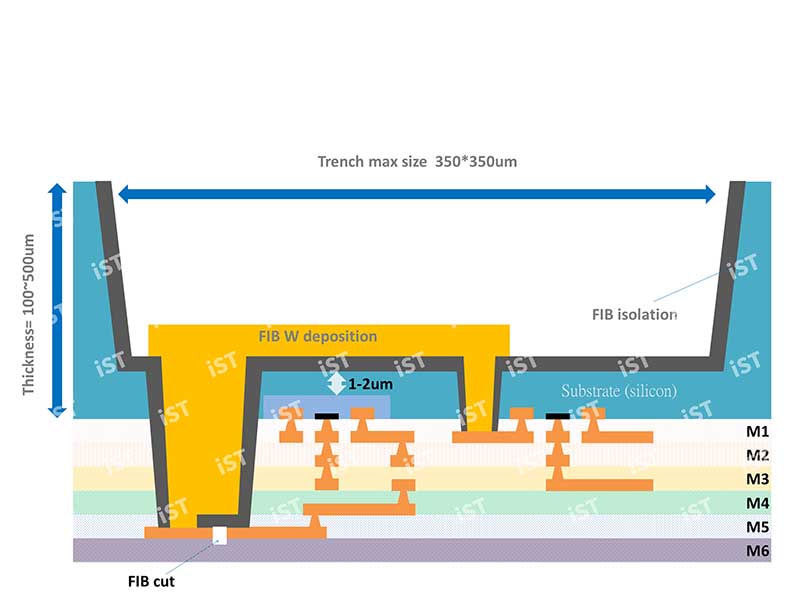

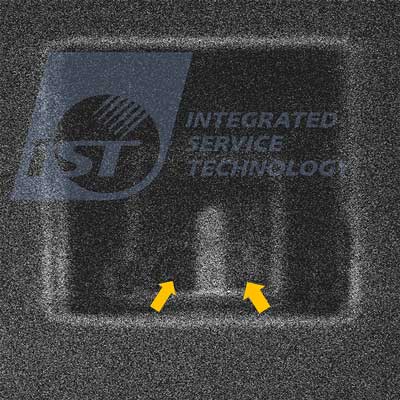

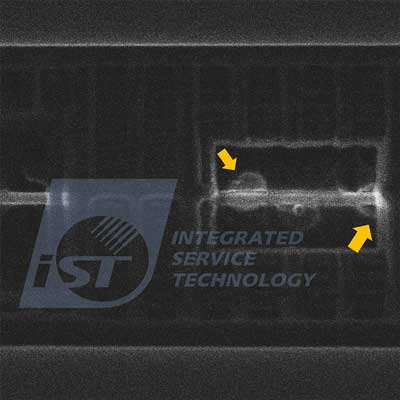

二、 晶背修補兩大關鍵技術- 前置處理Substrate層的厚度與End Point的停留位置

進入晶背(Backside)修補工程的第一個階段,首先面對的是Substrate層(Silicon);終端產品形式會決定包裝厚度規格,其晶片的厚度,通常由矽晶圓時的31mil,研磨至8~12mil,不過這樣的厚度,對微/奈米等級的FIB電路修補並無法直接開始手術,為此,我們將依照第一點的三大步驟佈局規劃,定義蝕刻範圍的「局部削洗Silicon層的減薄厚度」(milling silicon trench,Max size 350*350um),不過如何提高溝槽(trench)內表面平整度(參見圖二)以及判斷終點(End point)位置(參見圖三),避免過度蝕刻(over etching)(參見圖四),將是兩大關鍵技術;以7奈米為例,Silicon厚度保留在1~2微米為最佳(參見圖五),這是電路修補前的關鍵步驟。

圖五:晶背電路修補示意圖,建議Silicon厚度保留在1~2微米(um)為最佳。

三、 如何精準定位目標、清楚辨識電路?

先進製程,特別是7奈米製程的金屬與介電層的間隙、寬度、厚度,多為40奈米(nm)或以下,面對薄且小的工藝,精準定位目標、清楚辨識電路是最大的挑戰,而且電路修補的過程經常是以「秒」來計算,稍一失誤將前功盡棄。

該如何精準定位目標呢? 由於從晶背施工,以電子顯微鏡成像是無法看到線路,需先使用紅外線攝影機穿透並依靠四個角落來進行初步定位讓GDS對準晶片,再利用一個或多個參考點(reference point),多次定位以降低誤差,通常距離目標點最遠100微米(um)即可定位,不過越遠誤差就越高;建議選擇距離目標點20微米(um)內,約2*2微米(um) 可破壞區域做為定位點,實際誤差可降至150奈米(nm)。

四、 蝕刻參數與氣體的調校、避免過曝金屬層(Metal)

本文與各位長久以來支持宜特的您,分享經驗,若您想要更進一步了解細節,歡迎洽詢+886-3-5799909 分機6000 王先生Chino│Email: web_fib@istgroup.com