發佈日期:2025/11/27 SIPI訊號模擬

發佈單位:iST宜特

SIPI訊號模擬:高速設計為什麼非做不可?

你的高速產品跑得快,但是跑得穩嗎?在 GHz 時代,每一條線都可能是地雷。訊號延遲 10 皮秒、阻抗多 1 歐姆,都可能讓你的產品在量產前夕「翻車」。唯有透過 SIPI 模擬,才能在設計階段看見潛在風險,讓高速產品從「能動」變成「能順利量產」。

SIPI訊號模擬

SIPI訊號模擬

你的高速產品做過 SIPI 模擬嗎?在低速系統中,模擬或許只是錦上添花的工具;但跨入高速時代,任何細微的訊號失真或雜訊,都可能是產品上市的隱形阻力。SIPI 模擬能在設計階段預測並修正問題,從眼圖、抖動到 PDN 阻抗一次掌握,讓你不再後知後覺。

在現今數位高速設計的時代,「功能正常」早已不是設計成功的唯一標準。隨著訊號速率全面邁入 GHz 等級(如 PCIe Gen5/6、DDR5、USB4 等),任何微小的電氣問題都可能成為潛藏風險,導致數據錯誤、系統不穩,甚至使產品無法順利上市。

而最有效的預防方式,就是在設計流程中導入訊號完整性(Signal Integrity Simulation,簡稱SI)和電源完整性(Power Integrity,簡稱PI)模擬測試,預先找出潛在問題,從根本提升設計的成功率與可靠性。

本篇宜特小學堂將帶你了解為什麼高速設計必須導入SIPI 模擬的十大關鍵,並分享具體的導入流程,讓你的設計更穩定、更高效、更具競爭力,在問題發生前提早避開錯誤。(閱讀更多:AI高速訊號傳輸時代來臨!宜特最新解決方案助您搶佔市場先機)

一、SIPI 原理簡介

SI訊號完整性模擬(Signal Integrity Simulation,簡稱SI),是一項針對高速電路設計的預測性分析技術。透過準確建模與仿真工具,讓我們在 PCB 尚未製作前,就能預測訊號傳輸過程中的可能異常,並提早排除電氣風險。它可預測並消除訊號失真、干擾與反射;評估 jitter(抖動)、損耗、串音對系統穩定性的影響;確保訊號在高速環境下具可解碼性與一致性。

而PI電源完整性模擬(Power Integrity,簡稱PI),則著重於電源分配網路(Power Distribution Network,簡稱PDN)的穩定性分析,確保電壓供應平穩、雜訊最小化。它能預測電源平面雜訊、IR drop 與去耦電容配置效能,避免瞬態電壓波動影響系統運作。

因此,在高速設計中,唯有同時掌握 SI 與 PI 兩大面向,才能確保整體系統的穩定性與可靠性。

二、為何必須導入 SIPI 模擬?十大關鍵問答

以下我們將以問答方式,帶你了解 SIPI 模擬如何從根本提升設計成功率,並在錯誤發生前就化解風險。

Q1:為什麼高速電路容易出現訊號反射?

A: 當走線(trace)、過孔(via)或連接器(connector)產生阻抗不連續時,訊號會被反射回傳,導致波形失真。這在高速環境中特別嚴重,可能造成 eye diagram 崩潰 或接收端錯誤判讀。透過 SI 模擬(Signal Integrity Simulation),工程師能在設計階段就精確預測反射位置,並修正阻抗匹配,確保訊號穩定傳輸。

Q2:為什麼兩條高速走線靠太近會干擾?

A: 當走線間距過小,訊號會從一條線耦合到另一條,電磁場會互相耦合,產生串音干擾(Crosstalk)。這種「隱形干擾」會使資料錯碼或 BER 上升。模擬分析可幫我們看到這些「隱形干擾」,並提出最佳看到這些「隱形干擾」,並提出最佳間距與屏蔽建議,維持系統訊號完整度。

Q3:訊號長距離傳輸會衰減,怎麼補償?

A: 高速訊號會受到導體損耗(Conductor Loss)與介質損耗(Dielectric Loss)影響,造成波形振幅下降與眼圖閉合。SIPI 模擬能協助設定適當的 trace 寬度、介質材質,並評估通道補償技術(如 EQ、CTLE、DFE),確保訊號保持清晰。

Q4:模擬真的能預測「眼圖」嗎?提早知道能否通過測試嗎?

A: 可以。眼圖(Eye Diagram)是量測訊號品質最直觀的指標。透過模擬,我們能預測眼圖開口(Eye height / width)是否足夠,是否符合標準(如 USB4、PCIe Gen5),在實測前就能確認訊號是否達標,大幅縮短除錯週期。

Q5:如何確保時序準確、資料不延遲?

A: 在高速電路中,訊號傳輸的延遲與抖動會直接影響時序容差(setup/hold margin),導致資料錯位。模擬可以精確預測每個通道的 delay、skew、jitter 等參數,幫助設計者在 layout 前就確保所有位元都「準時抵達」。

Q6:差分訊號的穩定性要怎麼確保?

差分訊號(Differential Signal)的對稱性、耦合性、skew 都會影響其抗雜訊能力與穩定性。SI 模擬可以量化skew、common-mode noise這些參數,確保差分對在極端條件下仍能穩定運作。

Q7:SIPI 模擬能幫助通過協定驗證嗎?

A: 能。現代高速協定(如 PCIe、USB、DDR)都有嚴格的 SI 規範,包含 eye mask、Tx/Rx equalization、return loss 等。透過模擬,我們能在實驗前預測是否通過協定要求,減少實驗室反覆修改與驗證風險。

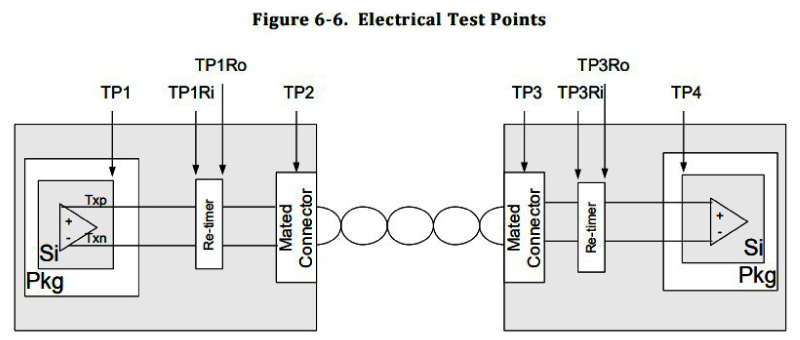

圖一:依照Universal Serial Bus 3.2 Specification定義USB測試環境及觀察點位置

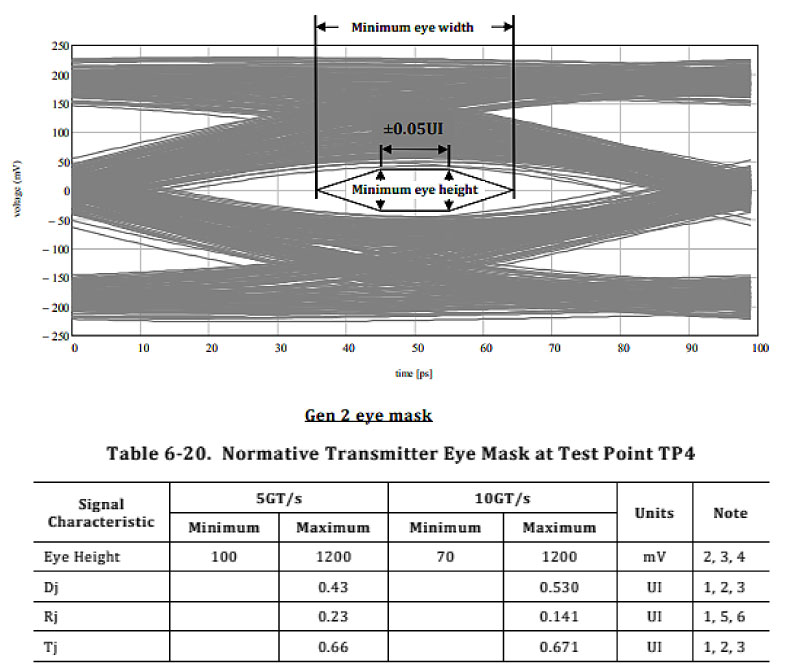

(資料來源: Universal Serial Bus 3.2 Specification)圖二:定義Eye mask在TP4位置的合格範圍

(資料來源: Universal Serial Bus 3.2 Specification)Q8:模擬能幫我節省成本嗎?

A: 絕對可以。若在 PCB 製造後或實驗室測試階段才發現訊號問題,返工成本往往是數倍甚至十倍以上。SIPI 模擬能在設計階段即找出潛在風險,避免重工與時程延誤,降低整體開發成本。

Q9:什麼是 PDN 阻抗?為何會影響供電?

A: 當 PDN(Power Distribution Network) 阻抗過高,會產生 voltage ripple 與 IR drop,使高速介面如 SerDes / DDR5 不穩定。PI 模擬可分析 PDN 的阻抗頻率響應,優化去耦電容配置、層疊設計,確保電源雜訊被有效抑制。

Q10:如何預測供電瞬態與 IR Drop?

隨著晶片切換頻率與電流需求攀升,瞬態電流變化劇烈,容易造成電壓下陷。

PI 模擬可預測不同負載條件下的 IR drop 與 transient response,提前修正 PDN 設計,避免供電不足導致 timing error 或 系統不穩。三、如何確認設計是否完善? SIPI八大觀測指標

(一)Eye Diagram(眼圖)

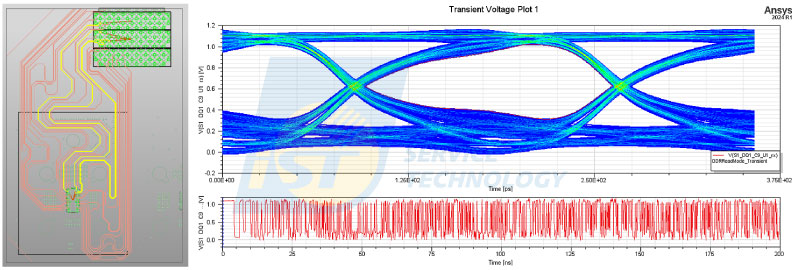

眼圖是把連續的數位波形疊在一起形成的圖像,用來評估高速訊號的穩定性與可靠性。它的形狀會受到 jitter(抖動)、損耗、串音與反射等綜合電氣效應影響。在SIPI 模擬中,工程師可在實際製板前模擬眼圖開口高度(Eye Height)與寬度(Eye Width),確認其是否滿足如 PCIe Gen5/6、USB4、DDR5 等協定所定義的 eye mask 規範。眼圖的開口大小,就是訊號是否可被正確讀取、能否通過合規驗證的首要門檻。

圖三:Eye Diagram眼圖分析

(圖片來源:宜特科技)(二)Jitter(抖動)

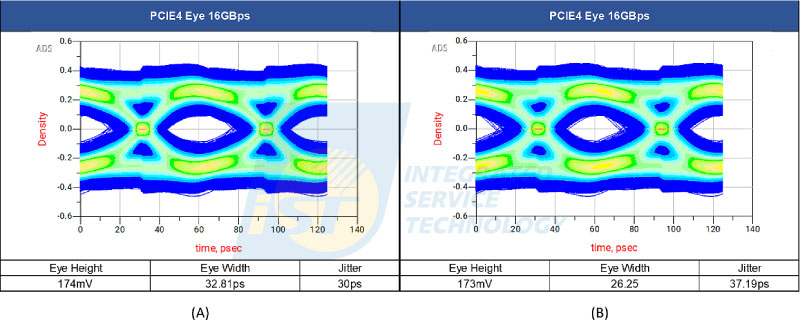

簡單來說,Jitter指的是訊號在時間軸上出現的晃動或偏移。可分為隨機性抖動(RJ)與確定性抖動(DJ)。在高速傳輸下,過多 jitter 會直接壓縮系統的時序裕度(timing margin),使資料誤碼機率大增。透過模擬,我們可以找出 jitter 的來源(如電源雜訊、反射或走線長度不一致)並提早修正,使設計具備更寬裕的容錯空間。

圖四:評估不同Jitter影響眼圖的情形,左A為TX DJ : 0.01UI , RJ : 0UI,右圖B為TX DJ : 0.05UI , RJ : 0.02UI 經過通道後RX端眼圖,可藉由模擬條件調整判斷Jitter及通道影響

(圖片來源:宜特科技)(三)Skew(時序偏移)

Skew 是多條訊號因延遲不一致而導致的時間差,尤其在差分訊號對與多位元並行傳輸中特別關鍵。若Skew 偏移過大,會影響資料同步與眼圖開口的對準。透過模擬,可量化走線長度、走線對稱性與信號 delay 差異,提供走線補償、via 結構對稱等設計建議,確保訊號同步。

(四)Impedance(阻抗匹配)

阻抗控制是穩定訊號傳輸的基礎。若走線、過孔或連接器的阻抗不連續,就會造成訊號反射。模擬工具可進行 2D/3D 結構建模分析,協助工程師掌控 trace width、layer stack、高頻材料選擇,確保整體阻抗一致。

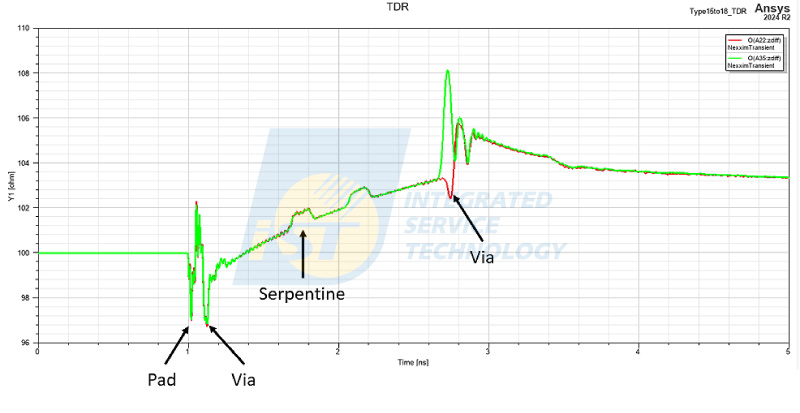

圖五:走線TDR結果,可藉由Delay評估造成阻抗不匹配的位置,修改結構設計,改善訊號反射問題。

(圖片來源:宜特科技)(五)S-Parameter(散射參數)

S-parameter 是頻域分析的基本工具,用來分析訊號在不同頻率下的傳輸特性。常見指標如 S11(反射)、S21(傳輸)可用來評估通道的反射與插入損耗。SIPI 模擬中,利用 scattering matrix 模型能預測整體通道在不同頻率下的傳輸效率,是驗證能否滿足協定規範(如 IL/RL mask)的基礎依據。

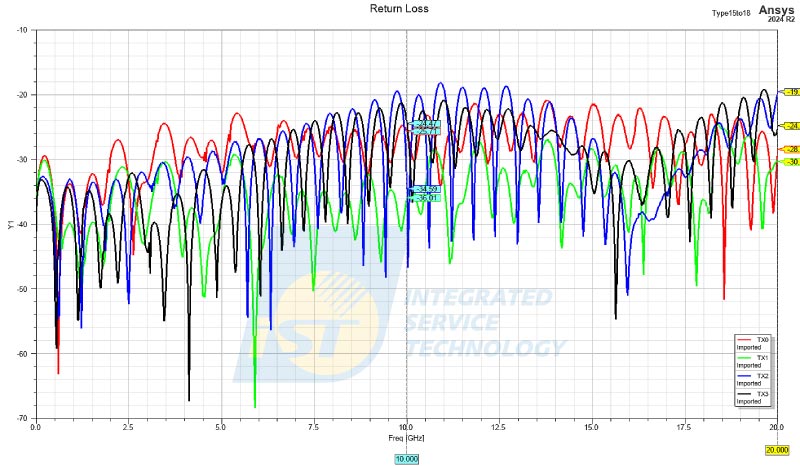

S11( Return Loss) ,代表訊號在發射端被反射回來的能量比率,是衡量阻抗不連續的關鍵指標。當訊號通過阻抗變化處(如過孔、連接器或 trace transition)時,就可能會產生反射。透過模擬,可協助我們預估反射行為並調整阻抗匹配設計,降低資料失真與干擾。

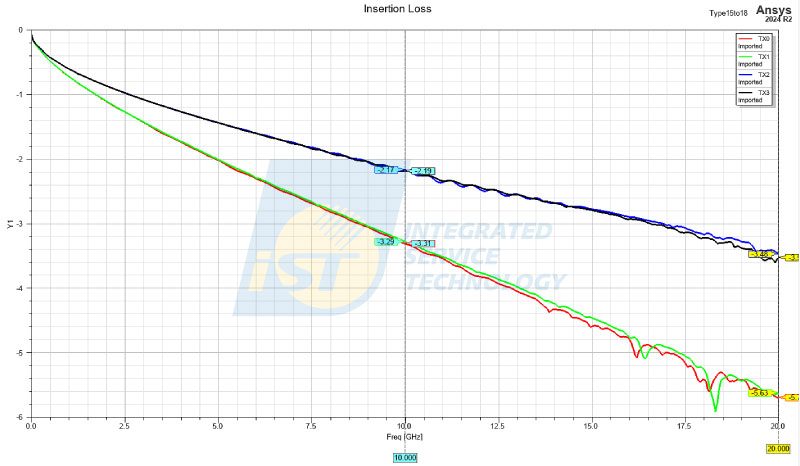

S21( Insertion Loss) ,則表示訊號從輸入端傳到輸出端時因介質與導體造成的衰減。損耗值愈大,訊號強度下降愈快,導致 eye diagram 崩潰。SIPI 模擬能在不同材料、走線長度與 routing 阻抗下量測 IL across frequency,協助選擇低損耗材質或補償設計,如加裝 re-timer、調整 layer stack,確保高速訊號仍能穩定傳輸。。圖六:S11可從結果圖評估是否需要對於走線設計進行修改(一般規範會定義需小於特定dB值)。

(圖片來源:宜特科技)圖七:S21可從結果是否over spec評估對於走線設計、長短、疊構或材料進行修改的必要性。

(圖片來源:宜特科技)(六)Crosstalk(串音)

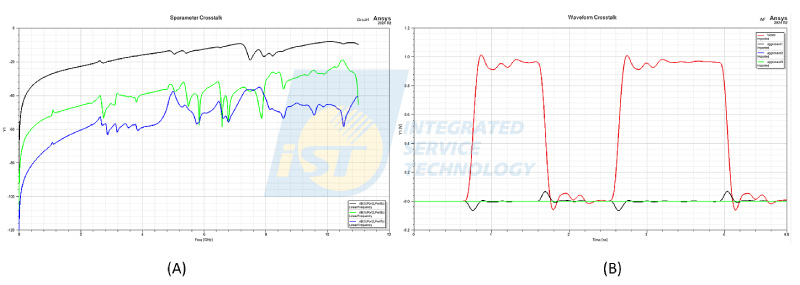

當兩條或多條訊號線靠得太近,彼此的電場與磁場會互相耦合,造成近端(NEXT)與遠端(FEXT)的串音干擾。模擬可幫助我們評估走線間距、層與層之間的影響,並最佳化走線設計(routing)、使用 guard trace(防護線)或 GND shielding(接地屏蔽)進行電氣隔離,避免系統錯誤與 BER(Bit Error Rate,位元錯誤率)增高。

圖八:分別從頻域及時域觀察受干擾的訊號線(Victim)受到的串音大小。左圖A為頻域結果,右圖B為時域結果。黑、綠、藍三條曲線分別代表不同干擾源(Aggressor)對Victim的影響情況。

(圖片來源:宜特科技)(七)BER(Bit Error Rate,位元錯誤率)

BER 代表每傳送多少位元中可能出錯幾次,是量化系統整體穩定性的重要指標。SI模擬能在各種 jitter 與損耗條件下預測 BER 階梯圖,判斷是否需加入FEC(Forward Error Correction/誤碼校正,簡稱FEC)或調整EQ(Equalization/均衡補償策略,簡稱EQ),保證訊號在極限條件下仍具可解碼性。保證訊號在極限條件下仍具可解碼性。

(八)Equalization(均衡補償)

為因應訊號經過長距離與高損耗通道所產生的衰減與波形畸變,系統常會配置 TX 預加強(Pre-emphasis)、RX 均衡(CTLE、DFE)等補償機制,能恢復波形。SIPI 模擬可測試不同 EQ 組合對眼圖開口的改善幅度,幫助選出最佳組合,平衡效能與功耗,特別適用於高速背板與 connector-rich 設計。

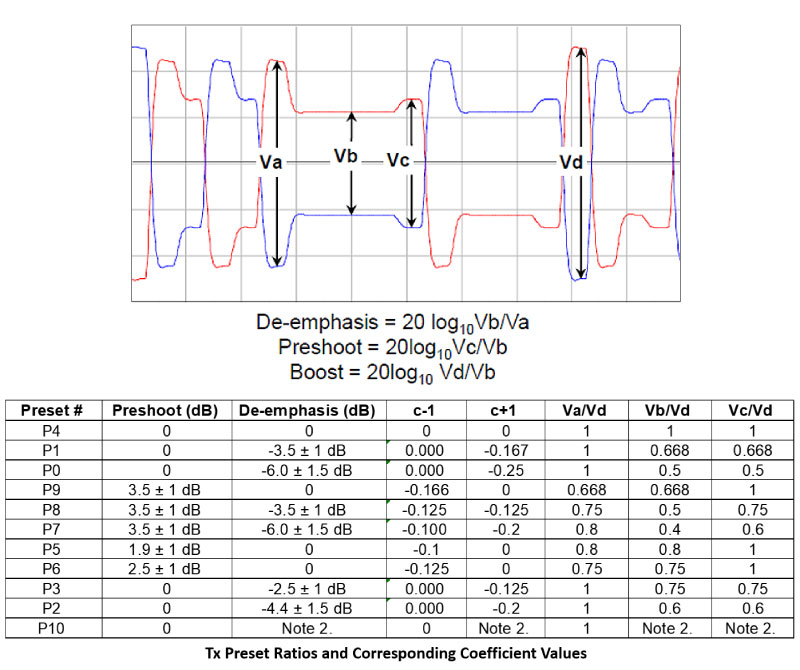

圖九:PCIe 發射端(TX)預設補償設定(Preset),在 IC 發射端進行高頻訊號加強,可提前補償通道中的高頻損耗,讓接收端波形更穩定。

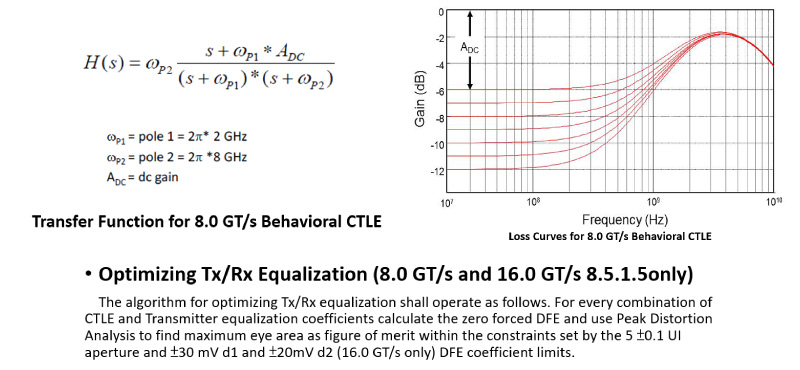

(圖片來源:PCI Express Base Specification, Rev. 4.0 Version 1.0)圖十:PCIe 接收端(RX)均衡設定中,CTLE 透過濾除低頻、強化高頻的方式修正訊號失真,但可能同時放大高頻雜訊;DFE 則可進一步抑制雜訊與干擾,改善 Crosstalk(串音)與 ISI(符際干擾)問題。

(圖片來源:PCI Express Base Specification, Rev. 4.0 Version 1.0)四、實施流程建議:從建模到驗證,全面整合

為發揮 SIPI 模擬最大效益,宜特建議依照以下步驟實施:

- 建立模型庫:蒐集元件(如 IBIS/Spice 模型)、互連(S-parameter)與電源分配網路(PDN)數據,建立涵蓋訊號與電源的完整模擬資料庫。

- 前期預模擬(Pre-sim):分析關鍵路徑的傳輸損耗、阻抗不連續與拓撲設計,同時評估 PDN 的阻抗分佈與去耦電容配置,確保電源穩定。

- 後期模擬(Post-sim):導入實際 layout 進行完整模擬,驗證 眼圖(Eye Diagram)、抖動(Jitter)、時序裕度(Timing Margin)及 PDN 噪聲(Power Noise)等關鍵指標。

- 設計優化調整:根據模擬結果修正 stack-up、routing、terminations、去耦電容(Decoupling Cap)位置與數量等設計參數,平衡效能與成本。

- 實體測試比對:進行 Lab 實測,與模擬結果比對,並持續調整模型精度,確保SIPI的模擬準確度。

在現今半導體與電子設計的競賽中,高速傳輸已從「加分項」成為「基本門檻」。導入 SIPI 模擬,能在設計階段即預先掌握潛在風險,減少反覆試錯與設計迴圈,不僅能降低開發時程延誤,也能減少實驗室測試次數,節省人力與設備成本。

本文與各位長久以來支持宜特的您分享經驗,若您想要更進一步了解細節

歡迎洽詢+886-3-579-9909 分機8890 林小姐│Email: HWBU_Sales@istgroup.com;marketing_tw@istgroup.com