發佈日期:2019/4/9

發佈單位:iST宜特

僅數奈米厚度的半導體元件的結構如何分析鑑定?

唯一有效的分析工具就是穿透式電子顯微鏡(TEM)。透過高精確度的定位TEM試片製作,再用高分辨率、高解析度的TEM分析,確認薄膜厚度與組成,以及界面結構。

2018年,一位來自美國賓州大學的教授,為了分析一種被動電子元件-憶阻器(memristor)的顯微結構而找上宜特,由宜特材料分析實驗室,協助該研究進行,此研究最終也獲刊於2019年二月號的國際著名期刊Nature Electronics。

什麼是憶阻器(memristor)?它又名記憶電阻(memory resistor),是一種被動電子元件,可在電子線路上用於保護重要電子裝置。結合二組憶阻器可產生相同於電晶體的功能,但體積更小,屬奈米級元件。以矽基材為主的憶阻器,其製程容易和目前的矽基IC整合,為下一代非揮發性記憶體的候選元件。

目前學研界對憶阻器的研究尚在起步中,很多理論和材料都在探索中。本月小學堂,就讓我們簡單介紹,宜特如何利用TEM結構分析技術,協助憶阻器的研究發展吧。

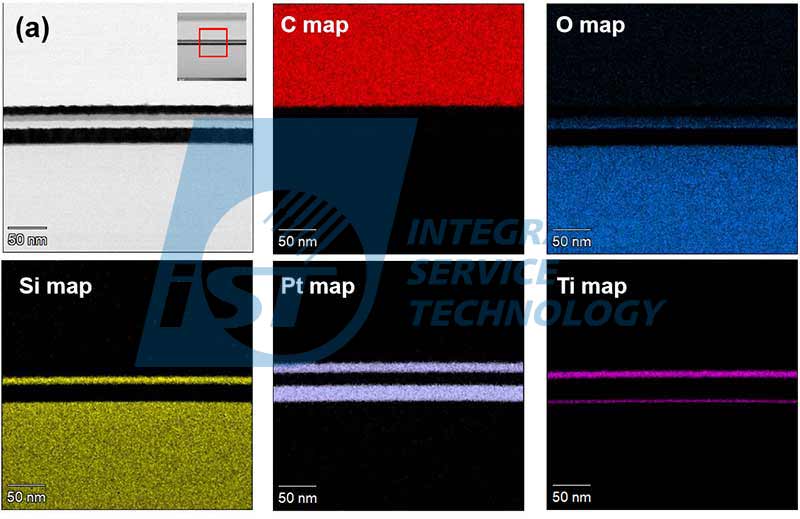

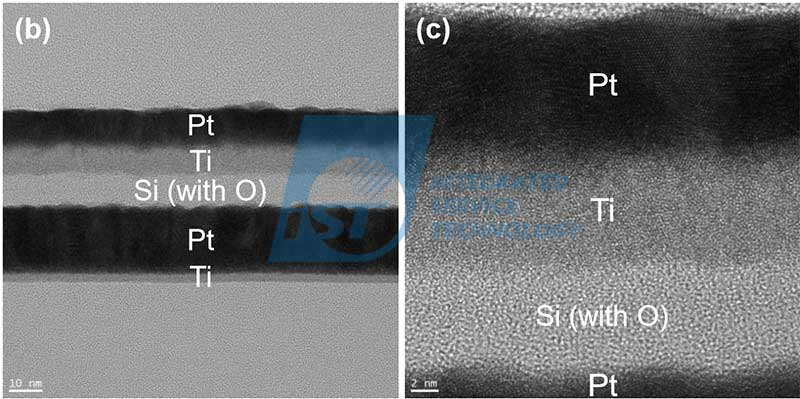

從下圖的TEM影像和成份分析結果顯示,憶阻器的主結構Ti/Si(O)/Pt總厚度只有約38 nm,而Si(O)絕緣層厚度只有7.2 nm,落在設計厚度 2 – 7.5 nm範圍內;而且是非晶質,確保電流的等方向性。薄膜之間的界面並非原子級的平坦度,但是非常完整,沒有任何空孔缺陷。

圖說: S1 Si憶阻器的橫截面TEM影像:

(a)EDS成份映像圖,元件結構從下往上,依序為黏結層Ti,下電極Pt,介電層Si (O),上電極Ti,保護層Pt。各層間沒有成份擴散問題。

(b)TEM 明場影像顯示各層堆疊情形。

(c)高分辨TEM (HRTEM)影像,影像對比的均勻性顯示沒有任何金屬奈米粒子在Si (O)層內。當界面足夠平坦,2 nm厚以上的Si層可以防止上下電極的針孔貫穿。上圖HRTEM影像顯示Si (O)層上下界面的平坦度約為0.5 nm。

(摘錄自:Nature Electronics , Vol. 2 , FEB. 2019 , 66–74 | www.nature.com/natureelectronics)

本文與各位長久以來支持宜特的您,分享經驗,若您想要更進一步了解細節,歡迎洽詢+886-3-5799909 分機6166 林博士 (weijui) Email: web_ma@istgroup.com