發佈日期:2017/3/29

發佈單位:iST宜特

IC發生高電阻值、漏電了,藍瘦香菇!客戶每天催解法(報告),頭殼抱咧燒,卻連異常位置在哪裡都還找不到!

是在XYZ 軸的哪兒?? 3D元件內的異常點(defect)該如何找起?

為因應電子產品對效能需求,因此有了3D晶片堆疊技術產生。但問題來了,這樣的技術所產生的元件,在失效後分析也更加困難,傳統的封裝元件只需在XY面的2D平面定位,即能有效找出失效位置,但3D元件還需要考量到Z軸位置,且晶片在上下堆疊重疊下,更不容易找到失效位置。

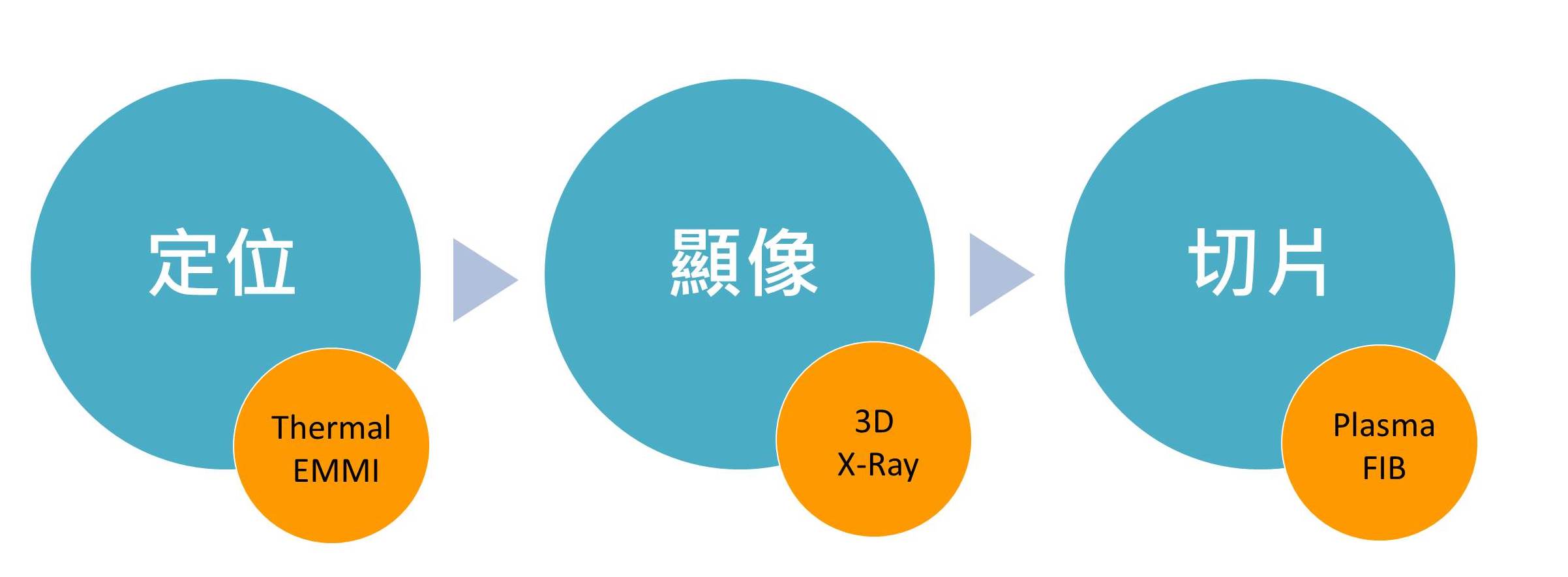

不過,別擔心,簡單三步驟,就能讓您3D元件異常點無所遁形。以下經典案例,3D元件發生漏電情形,宜特就是運用這三步驟,快速協助您找到產品異常點。

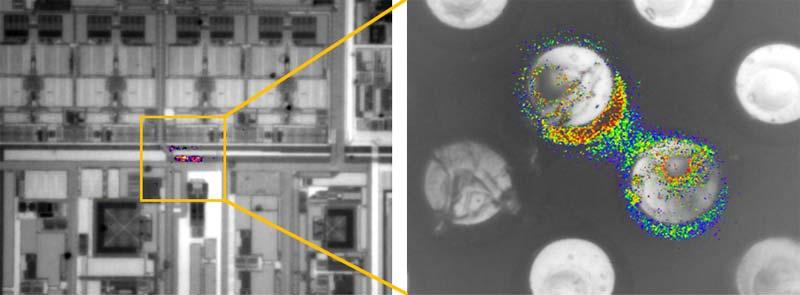

第一步驟 : 定位

在3D元件通電的狀態,且不破壞樣品的原貌下,利用Thermal EMMI故障點熱輻射傳導的相位差,偵測3D封裝的故障點深度(Z軸方向),快速定位故障點XYZ座標位置,並找到該異常點是在Solder ball(參見下圖)。

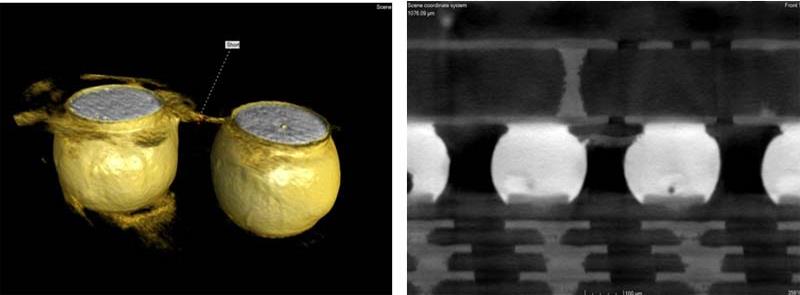

第二步驟 : 顯像

利用3D X-ray,將失效位置影像在非破壞的狀態下,呈現出3D立體圖與斷面圖。從3D立體圖(左下圖) 可以推估失效點是在Solder ball,再藉由3D斷面分析(右下圖),更清楚確認在solder ball靠近UBM層。

3D立體圖

3D斷面圖

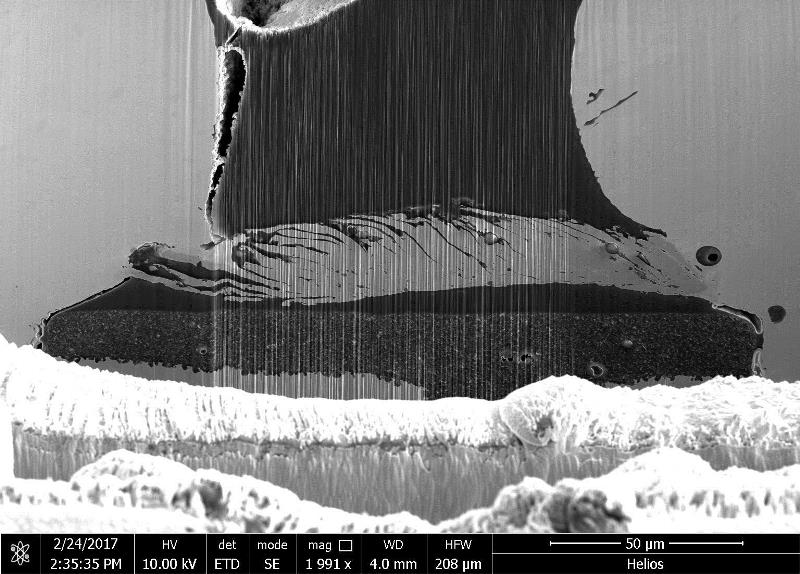

第三步驟 : 切片

3D元件在封裝材料(BOM)的搭配上應力較大,因此只要有外力,層與層之間容易爆開,所以必須選擇低應力工具。但若使用傳統人工研磨,應力會產生嚴重破壞,因此選擇,利用低應力Plasma-FIB將失效斷面切出並分析真因,找到元件中的兩顆Solder ball間發生RDL層橋接問題(參見下圖)。

本文與各位長久以來支持宜特的您,分享經驗,若您任何3D元件異常狀況不知如何分析,或是對相關知識想要更進一步了解細節,歡迎洽詢+886-3-579-9909 分機6767 陳先生 (Teron) │Email: web_ise@istgroup.com。