The Superiority of iST

Case Sharing

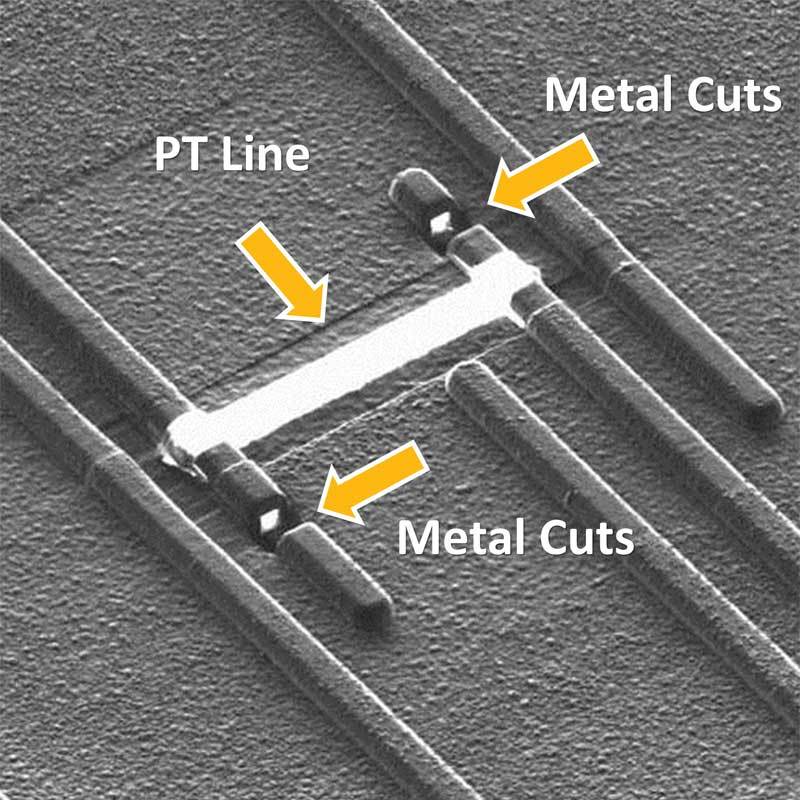

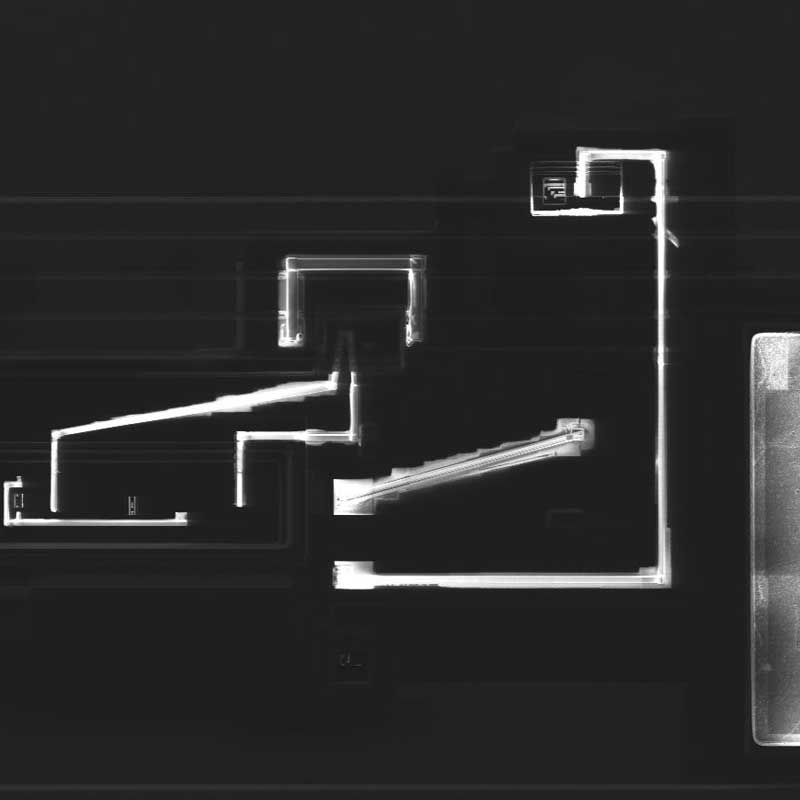

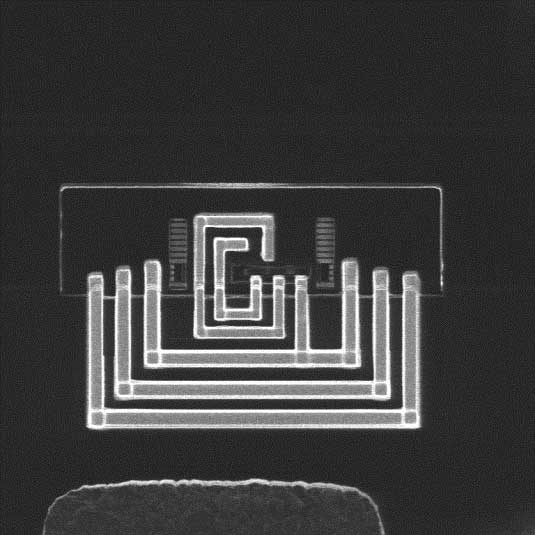

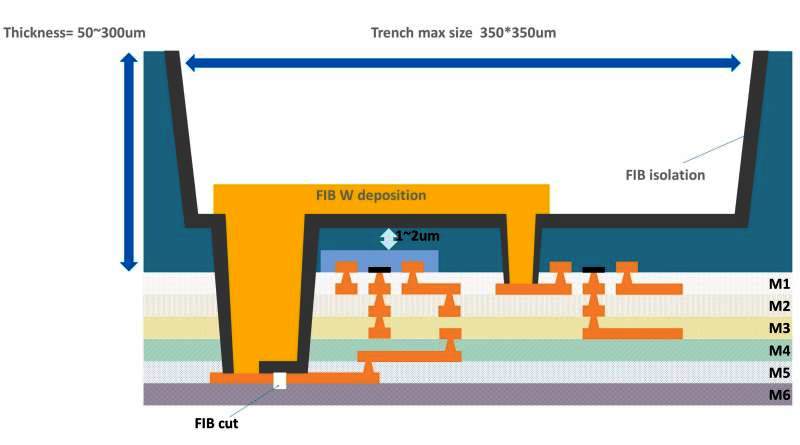

- Minimum Operation On 3nm Process Metal With 3.5nm Resolution.

- Maximum applicable to 8” wafers.

- Support CAD Navigation.

- Precision laser guided stage.

- Built-in infrared microscope for observing CMP layer and isolating silicon layer.

- Two choices for metal wires: tungsten (low resistance) or platinum (faster).

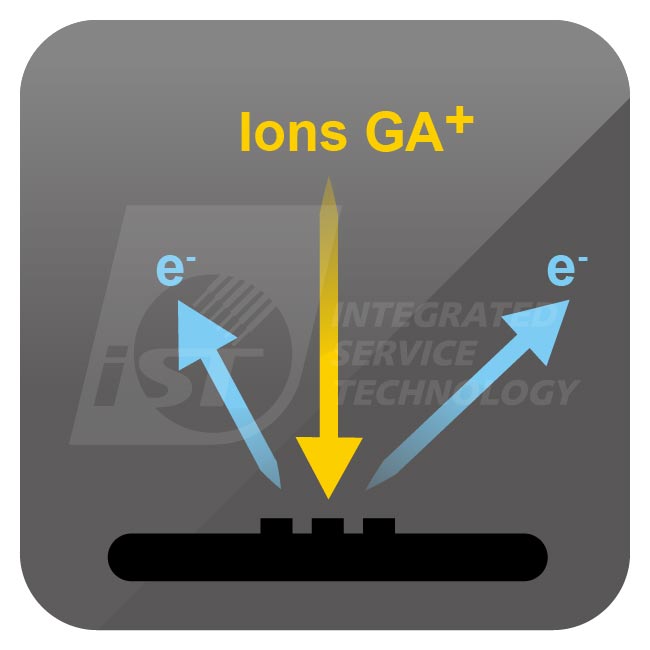

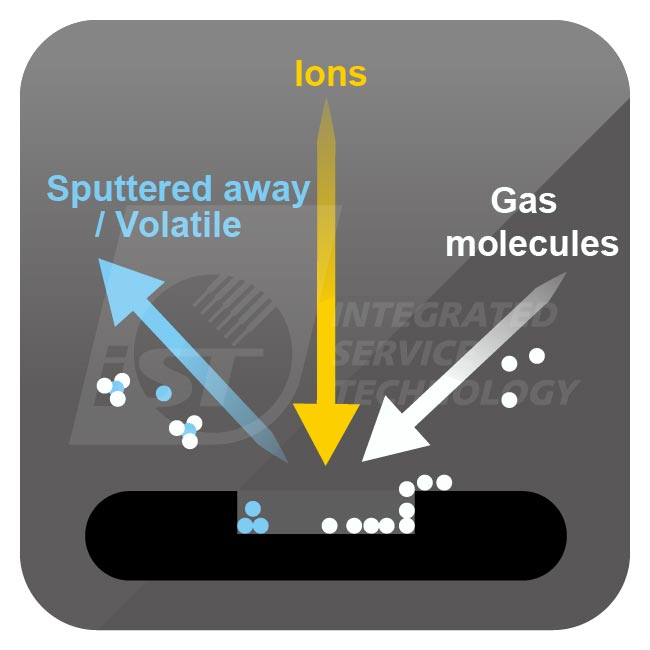

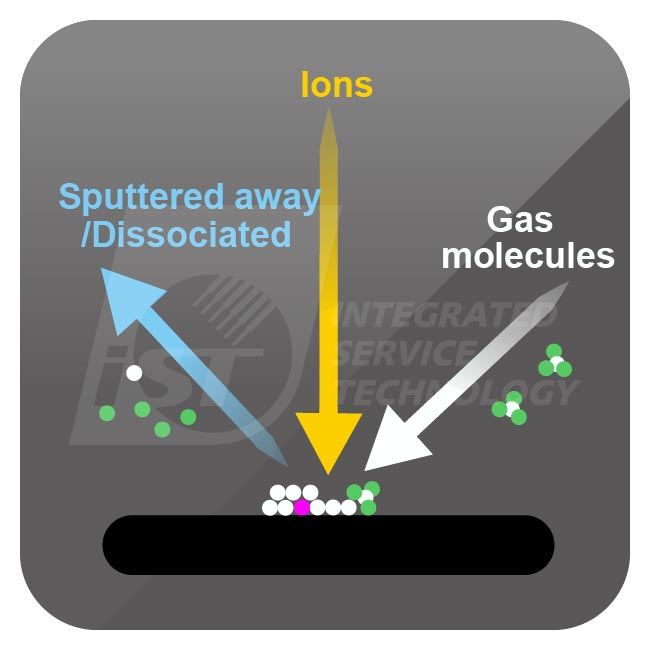

- Build with FEI DE/DX etching gas so as to increase the yield rate when apply to high aspect ratio and tighter circuit layout.

| Model | Capability Process | Capability Note |

|---|---|---|

| Centrios | 5nm |

|

| V400ACE | 7/16/22nm |

|

| 986-IET | 40/65nm |

|

| V600CE | 90/110nm |

|

| V600 | ≧130nm |

|

- Before FIB, test once more after decapsulation, wire bonding or packaging.

- Yield decreases if multiple modifications are made on the same IC.

- The resistance of conductor metal by FIB is higher than the original. Any low resistance conductor demand, please specify it on the service order.

- Suggest providing GDSII circuit layout to facilitate navigation (partial area or layer will be fine), this can help increase the yield.

Contact Window | Mr. Wang/Chino | Tel: +886-3-5799909#6000 | Email: web_fib@istgroup.com