Issued Date:2026/02/03PCR Memory

Issued By:iST

The price of DDR5 memory has surged by over 100%! As HBM production capacity squeezes the market in 2026, the margin for error at testing facilities has vanished. As the unit price of a single memory chip doubles, can your test interface ensure “zero damage,” “zero misjudgment,” and “zero frequent downtime” to protect your final profits?

PCR Memory

PCR Memory

The memory market is experiencing a historic surge. Driven by HBM3e/4 capacity constraints, contract prices for server-grade DDR5 have officially doubled between late 2025 and early 2026.

In an era where “chips are more valuable than gold,” every component entering the test station is far more critical and less tolerant of loss than ever before. Whether it is mechanical damage from excessive pressure or yield loss due to signal distortion, these seemingly marginal errors can lead to substantial financial impacts.

We have identified the most pressing challenges faced by testing houses and OSAT clients, offering strategic solutions to mitigate IC damage and ensure signal fidelity.

Can Your Test Interface Handle These Four Major Pain Points?

Q1: With DDR5 chips in short supply, how can we ensure “Zero Damage” during testing?

In Final Test (FT), the Pogo Pin acts as a “mechanical electrical switch.” It has been the standard equipment for semiconductor testing for decades, primarily providing a transmission path with elastic compensation. However, it relies on “rigid point contact.” During high-speed testing downward pressure, it easily leaves deep needle marks on the solder balls. Excessive contact pressure can even cause micro-cracks in the chip substrate, affecting reliability. If a batch of DDR5 is worth $10 million, a 0.5% scrap rate due to Pogo Pin damage results in a $50,000 loss.

iST Solution: Complete FT Testing Without Damaging the Chip

iST’s latest Rubber Socket (PCR) utilizes Pressure Conductive Silicone Rubber technology. With a low contact force of 15~50gf and elastomeric surface contact characteristics, it evenly distributes downward stress, ensuring no damage to the chip and saving high costs from memory attrition.

Q2: Inaccurate testing and signal distortion lead to “Good Dies” being misjudged. How to avoid the nightmare of overnight debugging?

Traditional Pogo Pins have complex structures—comprising a plunger, barrel, and spring—which lead to longer paths and higher inductance. This interferes with high-speed DDR5 signal transmission, causing good chips to be misidentified as failures. Once a yield alarm is triggered, engineers must immediately determine if the chips are truly defective or if the issue lies with the socket pins or signal distortion. Until the cause is found, current stock cannot be shipped, and the next batch cannot enter production.

iST Solution: Eliminate Misjudgment and Boost Yield

iST’s PCR thickness is only 0.5~1.2mm, offering an extremely short signal path. The contact resistance is stably below 30mΩ at 25°C, featuring stable FSR (Force vs. Stroke vs. Resistance) characteristics. This not only reduces downtime from repeated machine adjustments but also supports a high bandwidth of 40~50GHz, minimizing misjudgment caused by signal distortion. For high-priced DDR5, reducing the misjudgment rate by just 1% significantly protects profit margins.

Q3: Pogo Pins require frequent downtime for replacement and maintenance, especially under high-pressure and high-temperature conditions.

Traditional Pogo Pins are prone to breaking or accumulating solder residue (tin dross), requiring frequent downtime for disassembly and cleaning. This leads to high labor and component costs.

iST Solution: “Zero Frequent Downtime” to Gain More Time

iST’s PCR offers a lifetime of up to 100,000 mating cycles even in extreme environments (-40°C to 135°C). Its durability significantly reduces maintenance frequency, allowing production lines to operate 24/7.

Q4: The chips have arrived, but the test fixtures are stuck in customs. What to do about long lead times?

The complex structure of traditional Pogo Pins relies on precision parts often imported from abroad. When the supply chain is tight or customs are delayed, lead times can easily reach 4 to 8 weeks.

iST Solution: Fast Lead Time with Localized Production!

iST provides complete PCR hardware design, R&D, and production lines in Taiwan. From specification confirmation to delivery, the lead time is as fast as 1 to 2 weeks.

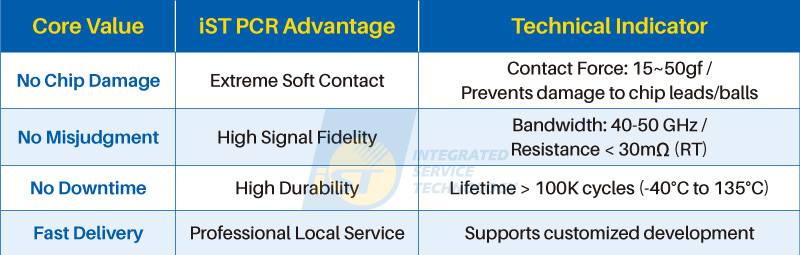

iST PCR Solves Your Pain Points: No Damage, No Misjudgment, No Downtime, Fast Delivery

In an era of skyrocketing memory prices, your choice of test fixture directly determines your gross margin and your work-life balance. iST PCR is designed for high-end memory testing, safeguarding your yield and maximizing efficiency.

Table 1: The Advantages of iST PCR

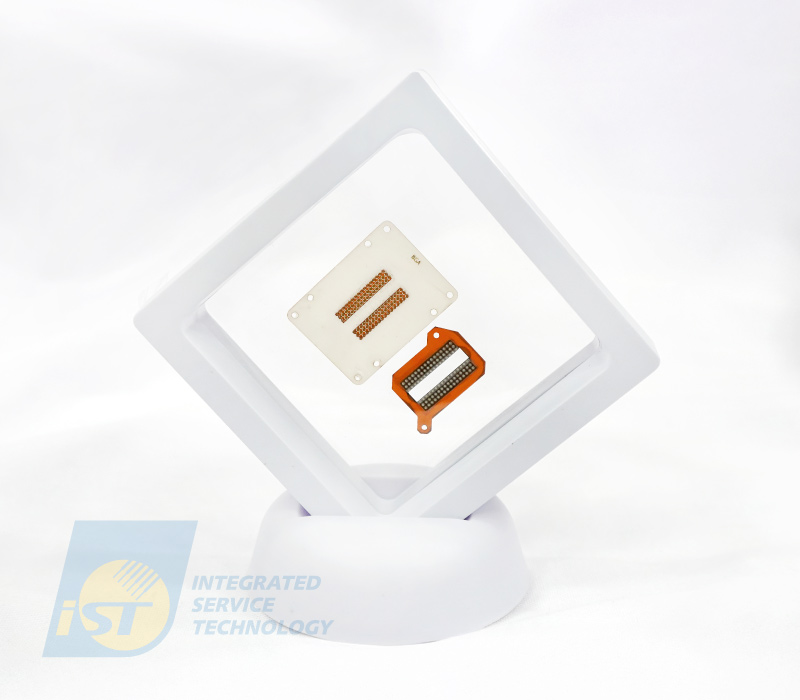

Figure 1: Product Photo of iST PCR-Memory

(Source: iST)

For further details, please contact Ms. Chen at +886-3-579-9909 Ext. 1065 Email: marketing_tw@istgroup.com