5G

拒當5G 時代的局外人: 相關封裝測試項目, 你準備好了嗎?

針對5G裝置的先進封裝需求,其可分為終端應用以及雲端應用兩個層面來探討:

終端裝置的高階封裝需求

終端裝置包含應用在手機以及筆記型電腦(NB)的部分,如以5G手機為例,其應用講求輕薄短小、傳輸快速,且整體效能取決於核心的應用處理器AP(Application Processor) 晶片。當然隨著5G高頻波段的使用,負責傳輸訊號的天線設計也須隨之改變。

以下將針對應用處理器與天線做進一步的說明:

1. 5G手機的應用處理器(Application Processor,AP)

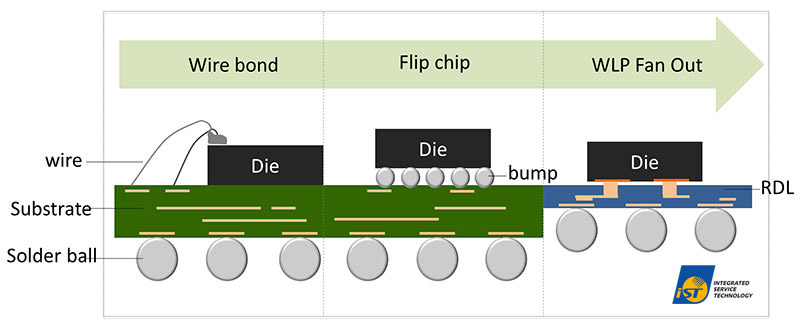

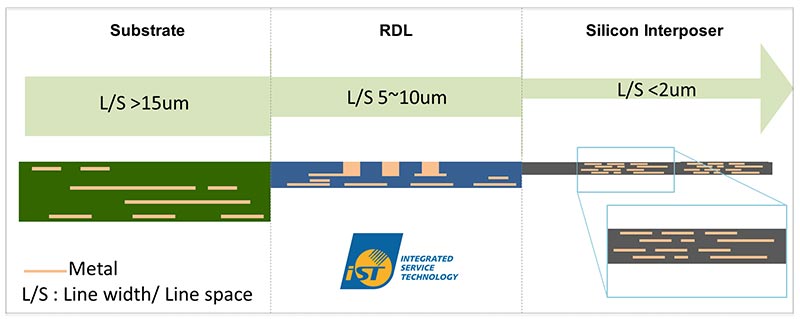

AP性能的提升除了晶圓製程的微縮外,就是依靠封裝技術的協助。其形式主要是以POP(Package on package)封裝為主,藉由POP的方式來堆疊DRAM能有效提升晶片間的傳輸效率並減少所需的體積。其連接方式從傳統的打線(wire bonding)、覆晶(Filp chip)一路演進到目前的扇出型(Fan-out)封裝。扇出型封裝主要是利用RDL佈線減少載板(substrate)的使用,如下示意圖

藉此減少載板的使用,間接達到效能提升、改善散熱、降低產品尺寸及成本的目的,因此在AP的IC選擇上,多以Fan out POP(Package on package)封裝型式為主。

2. 天線

隨著5G將高頻毫米波頻段導入商用,使得5G訊號從1GHz以下,延伸至超過30GHz,裝置對於天線的需求更勝以往,使得天線尺寸、路徑損耗以及訊號的完整性必須被加以考慮

- 天線尺寸:由於天線體積取決於頻率,隨著更高頻波段毫米波(mmWave)的使用,天線將能有效的縮小尺寸至毫米等級。

- 訊號完整性:透過增加天線數量進行發送及接受訊號,能使得資料傳輸的速度更快。

- 路徑損耗:高頻波段穿透性強,但穿透所造成的能量耗損以及干擾會使得有效傳輸距離變短。

因此在天線數量激增、可用面積維持不變的情況,天線封裝(Antenna in Package,AiP)封裝型式,則成為目前廠商的最佳解決方案,AiP主要採SiP(System in Package)或PoP的結構將RF晶片置入封裝以達到縮小體積、減少傳輸的距離以降低訊號傳輸時造成的耗損的目的。結構上可利用RF晶片的位置將結構區分成兩種,一種是包含在substrate內部的結構,另一種則是將RFIC置於substrate外側的結構。

雲端裝置的高階封裝需求

技術挑戰

1. 熱膨脹係數不匹配(CTE mismatch)

不同的材料具有不同的熱膨脹係數(coefficients of thermal expansion,CTE),隨著溫度的變化使得材料的膨脹狀況不一,因此會產生材料應力(material stress)。由於5G封裝內堆疊了多種異質晶片,應力釋放的過程將更容易導致裂痕或脫層的現象並影響晶片的運作。

「熱」永遠是產品可靠度的第一殺手,特別是同一封裝中納入不同晶片的溫度耐受度不一,晶片外部溫度、系統溫度也會產生影響。

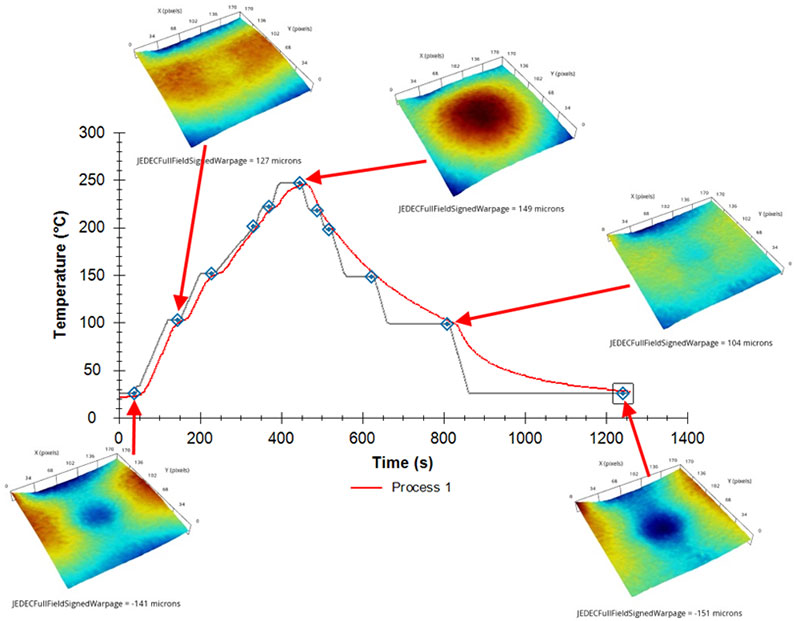

2. 翹曲(Warpage)

由於5G先進封裝異質整合晶片堆疊較以往複雜,且封裝體積有擴大的趨勢,容易導致substrate嚴重的翹曲(Warpage)。特別是在進行表面黏著技術(SMT)時,因高溫使得翹曲更加嚴重導致無法順利焊接於PCB板上。除此之外warpage也可能導致雙球(Head in Pillow)的現象,進而造成可靠度測試早夭的問題。

3. 其他

高功率、高效能的產品主要是利用2.5DIC、3DIC封裝,因此需考量散熱及warpage問題,通常會搭配散熱蓋(heat sink)的設計來同步解決問題,但因其重量較重,在SMT過程中容易將錫球壓扁導致短路(bridge)等問題。

5G先進封裝晶片驗證分析

基於5G 先進封裝晶片的特性,所以在研發設計階段,包括先進封裝晶片翹曲的程度、異質材料整合的材料分析、在錫球上的表面黏著(SMT)狀況,以及溫度變化下,是否對於錫球、矽中介層接合有所影響等,都需要進行細部驗證。

1. 嚴重翹曲導致SMT失效、測試問題

先進封裝產品內部設計複雜度提高、尺寸的擴大,導致產品翹曲程度變嚴重,其結果會影響SMT上件的困難度以及測試socket接觸不良等問題。

針對此問題,宜特備有量測翹曲的設備(Shadow moire),可模擬回流焊(reflow)過程中元件與PCB 翹曲(warpage)的程度,藉此調整SMT參數設定,確保SMT過程中有良好的焊接品質。

2. CTE mismatch驗證

元件在長期運作的狀況下,因環境溫溼度的改變,材料交界處常因CTE mismatch而產生內應力,進而造成脫層及裂痕影響元件的運作。可藉由進行環境可靠度的測試,包括uHAST、TCT、Multi-reflow等模擬實際使用的狀況,以確保未來在變更材料、改變設計的狀況下,元件依舊能良好的運作。

對此宜特提供可靠度測試規範的諮詢,以及失效後一連串分析的服務,以協助客戶釐清元件異常的可能原因

3. 先進封裝結構複雜,難以用常規手法檢測

封裝結構的改變,導致進行可靠度驗證後,針對脫層等無法被電測出的異常難以用常規的手法(2D xray ,SAT ,FIB ,etc)直接進行檢測。對此宜特可針對不同的封裝結構,提供完整的建議,例如2.5D IC封裝進行reflow後確認散熱膏是否有脫層等。