発行日:2018/8/8

発行者:iST宜特

人気沸騰中のMOSFETパワー半導体チップ、どうしたら効果的にRDS(on)(オン抵抗)を下げられるのか?

MOSFETは電子製品において「スイッチプラグ」の役割を長きにわたって担ってきました。そのスイッチング速度が早く、低入力抵抗および低効率損失の特性ゆえ、大電流にも耐え、回路スイッチング効率も高いので、MOSFETがパワーデバイスにおいて重要な役割を果たしています。

そこでMOSFETメーカー各社は皆、高効率の電力変換、低効率損失を目標としています。この目標に達する近道が、RDS(on)(オン抵抗)を減少させるという方法なのです。

Rds(on)は幾つかの抵抗で構成されています。その内訳はソース(Source)側の接点抵抗Rcs、N+本体抵抗Rn+、チャンネル抵抗Rchannel、集積(Accumulation)エリアの抵抗Ra、電界効果地域 (JFET region)の抵抗RJFET、ドリフト領域(Drift region)の抵抗Rd、基材抵抗Rsub、ドレーン(Drain)側の接点抵抗Rcd、パッケージ抵抗総和Rpackです。

それでは、あまり多くの開発コストをかけずに、どのようにしてRDS(on)(オン抵抗)を下げられるのか?宜特から大きく分けて三つの手法を提案させていただきます。

一、シリコンプロセス(Si Process)および設計側(Design)から着手

この方法は過去10年にわたって努力されているもので、iST宜特は各MOSFET大手メーカーが近年各種方式の低オン抵抗MOSFETを開発していることを確認してきました。例えば、インフィニオン(Infenion)のCoolMOSは多層エピタキシャル積層技術を利用、STマイクロエレクトロニクス(STMicroelectronics)のMDMesh、東芝(Toshiba)のDTMOS、フェアチャイルド(Fairchild)のSuperMOSなどは、ディープトレンチ充填技術を利用したものです。また、オン・セミコンダクター(OnSemi)のUltiMOSは、ディープトレンチ充填にLiner oxideを併用した設計でSuper Junctionを形成、N-type Epi濃度を向上させつつ、空乏層の深さを保つことでRDS(on)を低下させています。特にインフィニオンのCoolMOSは、1998年のリリースから現在に至るまで、常に業界において肯定的な評価を得ており、特に過去3年にわたって16億チップを超えて出荷されています。

二、パッケージ(Package)側での改善

ICがパッケージプロセスに送られる際、クリップボンド(Clip Bond)と拡散ハンダ付け(Diffusion Solder)の導入によって、銅クリップ(Clip)を使用して電流パスを拡張、ゴールド線(Gold wire)に替わって導線抵抗を減少させ、異質金属間では金属化合物(Intermetallic compound)によって金属間抵抗を下げ、RDS(on)(オン抵抗)も下がります。

三、チップ本体の厚さを減少させることで対処

前述のようにRDS(on)は、一連の抵抗値の総和で決まり、そのうちの一部はRsubによって決まります。このRsubはウェハー本体の混合物濃度濃度および厚さに関連しており、チップ本体の厚さを小さくすることでRDS(on)(オン抵抗)を減少させることができます。そのため近年、市場においても「ウェハー薄化」技術でウェハーの厚みを薄くする努力がなされています。

この第3ポイントであるチップ厚の低減に関して、iST宜特が最近立ち上げた新事業「MOSFETバックエンドウェハー製造プロセス整合化サービス」において、顧客のニーズに従った「ウェハー薄化」サポートしています。この「ウェハー薄化」においては、非常に精密に薄くすることが、技術面でのとても高いハードルとなります。

まず、非常に薄く加工すること自体がとても難度の高いものとなります。薄化後のウェハー周辺部分は容易に歪みやすく、その後のバックエンド製造プロセスにおける困難度を上げてしまいます。ウェハーが容易に歪むと、出荷時の破損、更には自動操作ができない場合の手動操作の際の破損を招くことになります。これらの問題を解決すべく、iST宜特はTAIKOテクノロジーを採用し、ローカル的な精密グラインディングを可能としました。ウェハー周辺部に太鼓の枠状のものを残しながら、ウェハー中心部を高精度で研磨することにより、ウェハーの歪みを回避します。現在50ミクロン(um)薄化が、複数のクライアントにおいて検証済みで量産に入っており、良品率は99.5%に達しています。また、37.5ミクロン(um)、25ミクロン(um)薄化に関しましてもエンジニアリング検証を進めています。

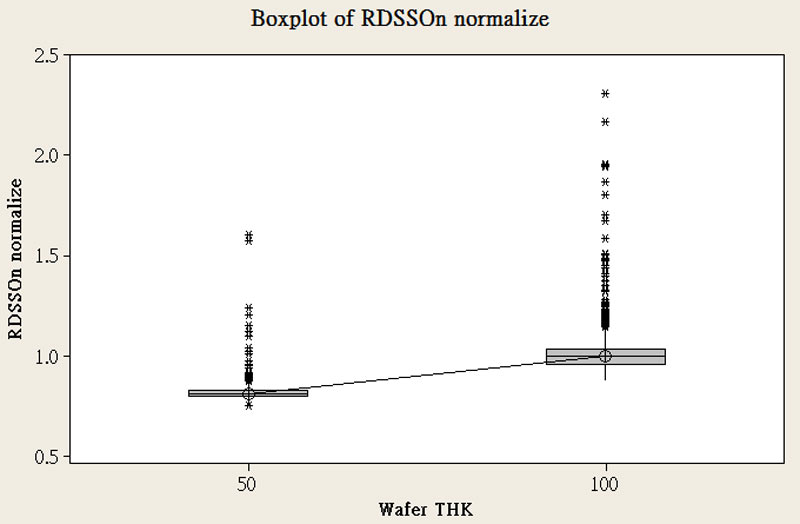

次に、非常に「精密」な薄化データを得るという面においても成果がありました。最近iST宜特は、RDS(on)(オン抵抗)の減少を目的として、ある顧客から、100ミクロン(um)および50ミクロン(um)へのウェハー薄化要求を受けました。RDSiST宜特は、エッチング技術を駆使することにより、ウェハーの ウェーハ内の厚さ変動TTV(Total Thickness Variation)を3ミクロン(um)以内に制御し、良好な均一性を得ることが出来ました。さらに当社は、ウェハー厚さを100ミクロン(um)から50ミクロン(um)にすることにより、RDS(on)(オン抵抗) を19%減少させる効果を発見しました(注1)。この方法では、設計上の変更は何ら必要とせず、ウェハーのファンドリー工場およびバックエンドパッケージ工場での生産条件の変更を一切必要としません。

図の解説: iST宜特はウェハー薄化技術により、ウェハー厚さを100ミクロン(um)から50ミクロン(um)へと減らした結果、顧客ニーズに対応してPower MOSFETのオン抵抗RDS(on)を19%減少させました。

当然ながら、iST宜特は薄化技術をさらに研究し続けており、既に15umの薄化技術を実現しています。図においてシリコンウェハーが蝉の羽のように薄く、光も通す様子を観察することが出来ます。白色光源を照らすと、ウェハーは赤い光を発しています。iST宜特は、Power MOSFETにおける更に低いオン抵抗を実現させるべく、顧客からの継続的なニーズに従い、顧客との協業関係を推し進めてまいります。

區塊

Click this link or the image above to view the 15 um wafer thinning video

注一:滿足MOSFET需求 英飛凌CoolMOS系列性價俱佳,賴品如,2018/6/27,https://www.digitimes.com.tw/tech/dt/n/shwnws.asp?CnlID=13&Cat=20&id=535181,2018/7/24 visited.

注二:ここでは、ウェハー電気特性測定(CP, Chip probe)の結果のみ示されています。図での比較はNormalizeの結果です。

以上、宜特の関連技術を紹介いたしました。貴社におきまして、RDS(on)(オン抵抗)低減のニーズまたはウェハー薄化のニーズがございましたら、+81-72-859-6601 ITC(代理店) 山本さん、+886-3-5799909 內線5888 游氏(Stan) │ Email: web_sp@istgroup.com , marketing_tw@istgroup.comまでお問い合わせください。