發佈日期:2023/3/7 晶片封裝

發佈單位:iST宜特

大型封裝廠處理量產品已應接不暇,延宕小量工程樣品,封裝資源怎麼取得? 晶片封裝

在研發階段取得試產品:晶圓/晶片後,大多必須透過封裝製程,才能進行後續的工程驗證。晶片封裝

而近期宜特觀察到,越來越多客戶,特別是學術研究單位,找上宜特進行工程驗證時,會先尋求宜特協助進行「工程樣品快速封裝」; 最大原因就在於大型封裝廠處理量產品已應接不暇,學術研究單位需要的少量研發工程樣品封裝需求,無法承接,因此找上宜特尋求協助。

為了可以讓客戶與學研單位拿到工程封裝品,宜特在20多年前即已成立快速封裝實驗室,每年替半導體客戶、學術研究單位完成數十萬顆實驗性工程封裝IC樣品。

本期宜特小學堂,將與您分享,宜特快速封裝實驗室,實際上是如何運作,讓您順利拿到工程封裝樣品;特別是針對系統級構裝((System in Package,簡稱SiP)、多晶片模組(Multi Chip Module,簡稱MCM )、四方平面無引腳封裝(Quad Flat No-Lead,簡稱QFN)等特殊封裝形式在進行故障分析前的樣品前處理,快速封裝服務如何派上用場,克服測試瓶頸。

晶片封裝

晶片封裝

一、 透過宜特公板封裝,快速取得工程樣品

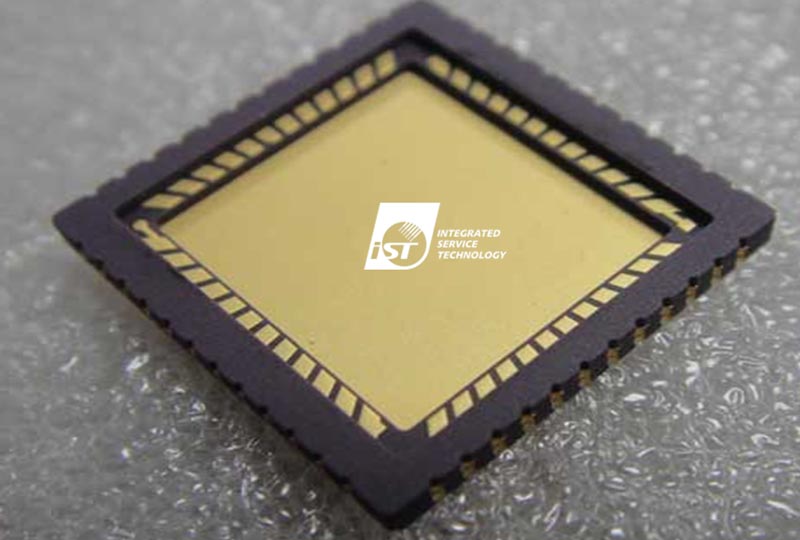

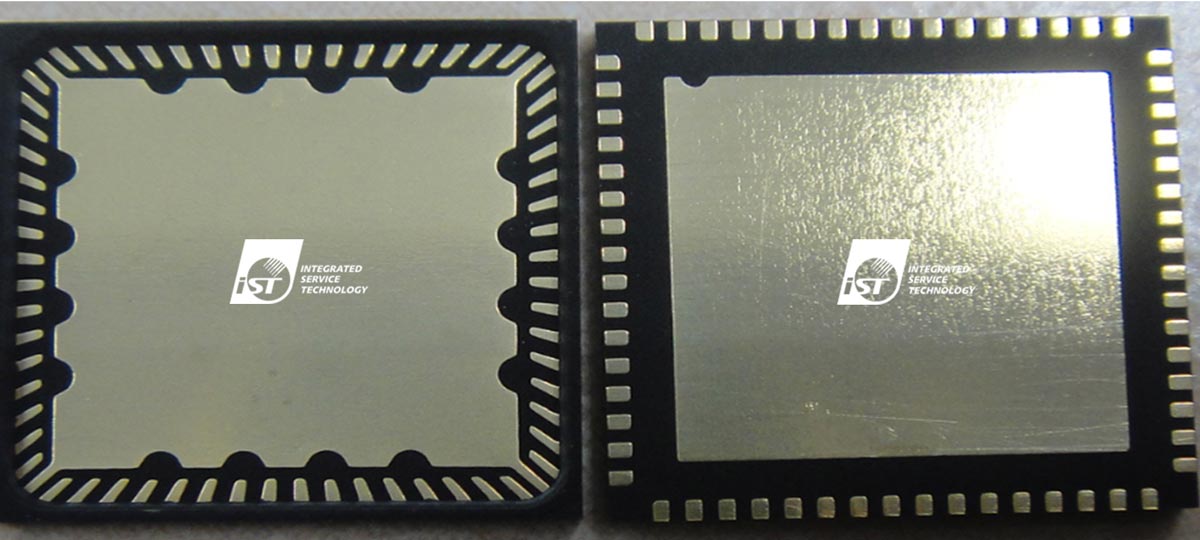

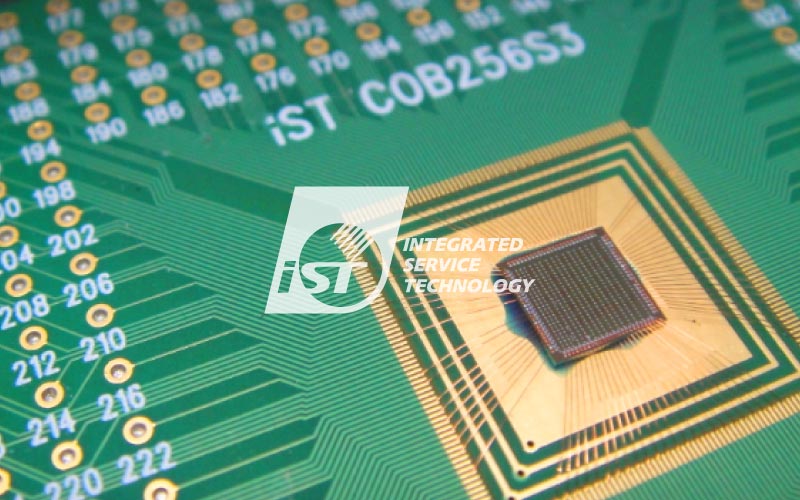

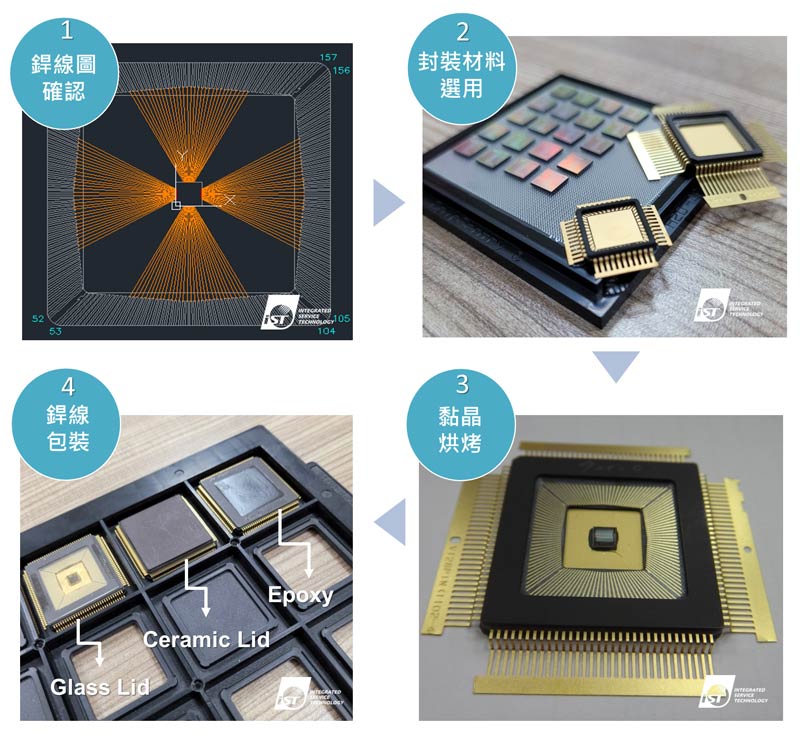

傳統量產品的封裝多使用導線架(Lead frame)與載板(Substrate),封裝製程多達20-30道,交期從3天到數周不等。而針對實驗性的工程樣品,宜特快速封裝實驗室則是透過陶瓷(參見圖一)、塑膠預成型(Plastic Pre-mold)(參見圖二)等材料,或公版COB/Socket整合樣品製作(參見圖三、圖四),精簡製程只需4道(參見圖五)。

值得一提的是,目前晶片封裝多以銲線驗證前提下,宜特公板結合共用與整合性測試環境的優勢,提供包含48/64/256等腳數規格(圖三、圖四),簡易完成可供驗證的樣品,快速進行功能驗證。

首先,第一步是封裝銲線圖確認。您可以提供封裝廠的銲線圖,或是將晶片資料提供給宜特,宜特將選用適合規格材料後,繪製出封裝銲線圖,確認無誤即可進行正式樣品作業。接著,依據客戶需求,使用導電或非導電膠,黏貼晶片在封裝材料上,再依照晶片規格,選用適當線材、線徑進行銲線作業。

最後因應客戶測試或使用方式,宜特可提供玻璃蓋、陶瓷蓋或是使用封膠方式保護晶片與銲線,即可讓您取得封裝樣品,供後續工程驗證使用。

二、 多晶片封裝驗證神助功:IC Repackage移植技術

當IC發生defect時,想分析其中一顆元件的異常狀況,又礙於SiP、MCM、MCP、BGA內部打線或基板線路互聯的關係,將導致電性測試時,容易受到其他Chip或元件影響,造成判定困難,甚至無法判定。

透過宜特研發出IC Repackage移植技術,可將SiP、MCM、MCP、BGA等封裝體裏頭,欲受測Die移植出來,送至宜特快速封裝實驗室,透過您提供的基板(客供基板,圖六)、或是由宜特協助您客製基板(圖七),進行重新黏晶焊線(圖八)及封膠切割/植球(圖九)成您所要求的Package型式,即可進行後續各式電性測試(閱讀更多: IC Repackage移植技術 助先進封裝晶片檢測無礙)

三、複雜封裝工程樣品,如何進行樣品前處理?

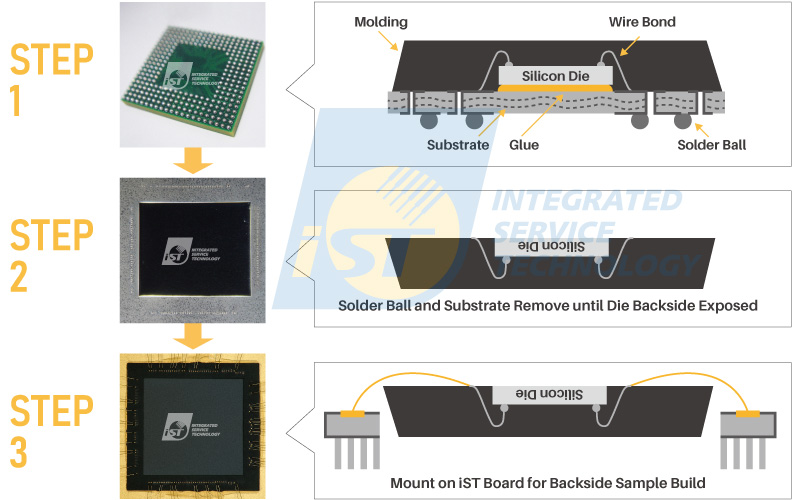

IC設計要進行後續功能性測試、可靠度測試或故障除錯前,必須針對待測樣品做處理。而樣品前處理的技術,對於後續功能測試是否準確、缺陷是否容易找到,都扮演關鍵性重要角色。傳統樣品前處理手法不外乎是透過IC開蓋(Decap)或研磨 (Front-side Polish )手法;從封裝體(Package)正面透過化學/雷射蝕刻(Chemical/Laser de-capsulation)露出正面,或膠體背面研磨至晶片裸露,或如前段提及,透過取Die進行Repackage移植的樣品前處理方式,

不過,在封裝線材日漸複雜的狀況下,重新銲線的風險提高,原始封裝的晶片銲墊經過化學蝕刻後將更為脆弱.後續故障分析也會因晶片結構層數過多,需要由晶背來釐清的比例增加。

宜特快速封裝實驗室也可藉由協助您,移除阻礙背面觀測的基板,並以橋接的方式,將指定位置銲點引線出來後,再透過EFA設備,從晶背得到清晰異常位置,進一步定位進行分析。

本文與各位長久以來支持宜特的您,分享經驗,除了快速封裝外,宜特實驗室也可提供樣品切割(wafer saw)、黏晶(die attach)與銲線(wire bond)等服務,也可配合您的晶片與客製化基板提供先進覆晶(flip chip)封裝服務,以利後續您進行ESD/OLT等分析驗證一站式(One-stop Solution)的高品質服務,有效縮短測試樣品的製作時間。若您有相關需求,或是對相關知識想要更進一步了解細節,不要猶豫,歡迎洽+886-3-579-9909分機6861陳先生(Peter)│ Email: ist_assy@istgroup.com;marketing_tw@istgroup.com