發佈日期:2022/6/28先進封裝焊點異常,

發佈單位:iST宜特

板階可靠度試驗結果Fail了,長官要你Debug,

如何使用簡單三步驟,快速找到異常位置呢?

板階可靠度(Board Level Reliability,簡稱BLR )是國際上常用來驗證焊點強度的實驗手法,透過將模擬元件組裝於PCB,重現出可能會發生的錫球焊接問題 (深入閱讀: 板階可靠度BLR對IC設計工程師有多重要?)。

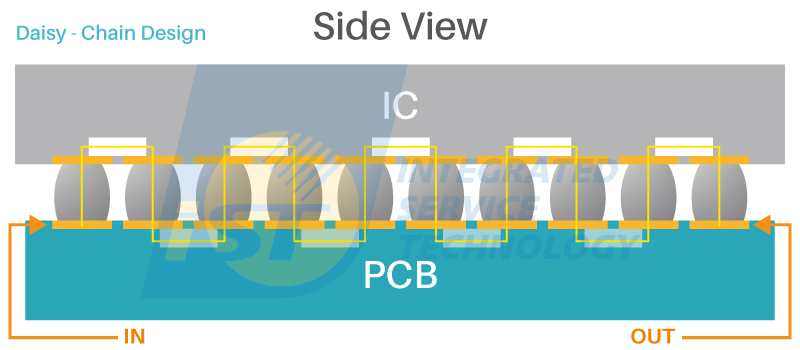

BLR的第一步,需要先進行菊花鍊(Daisy Chain)設計,將您的待測樣品元件與電路板連結的各個焊點形成網絡,藉此即時監控每個焊點良率,可成功得知各個錫球焊點是否失效,更能準確擷取失效的時間點,及早進行改善。

先進封裝焊點異常

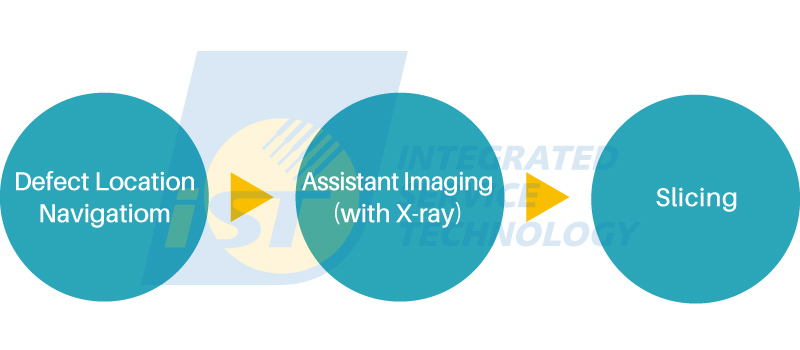

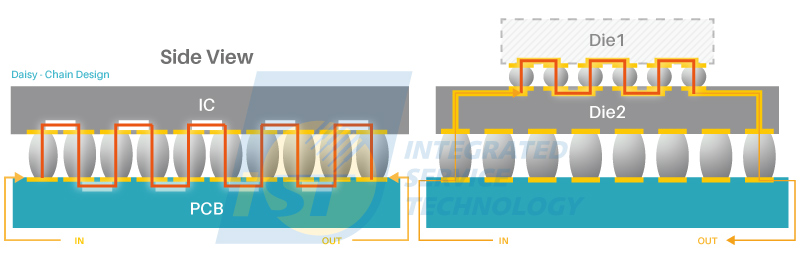

一、一般封裝樣品,利用二分法進行走線電性測試

在完成板階可靠度試驗後,若實驗後仍保有電性(Leakage/Short),第一步驟,宜特實驗室會先使用如Thermal EMMI(InSb)電性熱點(Hot Spot)測試機台,定位故障點XY座標位置。第二步驟,利用非破壞式的X-Ray/3D X-Ray顯像。第三步驟,可選擇使用較低應力的Plasma-FIB,或是使用研磨(Cross-section polish)搭配SEM的方式,將失效斷面切出並分析真因。 (延伸閱讀:如何釐清是否為封裝缺陷造成IC異常) 。

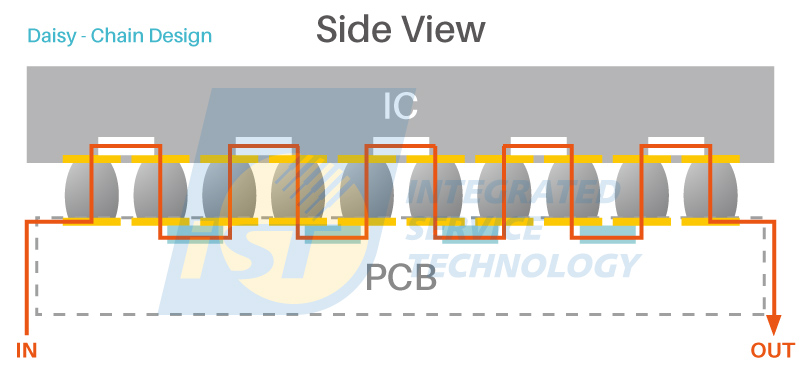

若異常現象為「開路(Open)現象」,因Open已無電流流過,無法使用熱點分析定位異常位置。必須在第一步驟「定位」前,先將樣品進行破壞性的水平研磨製備,從PCB測試板端水平研磨至Daisy Chain走線裸露後(圖三),接著,透過「二分法」(圖四),進行走線的電性測試,找到異常的相對位置(定位)。

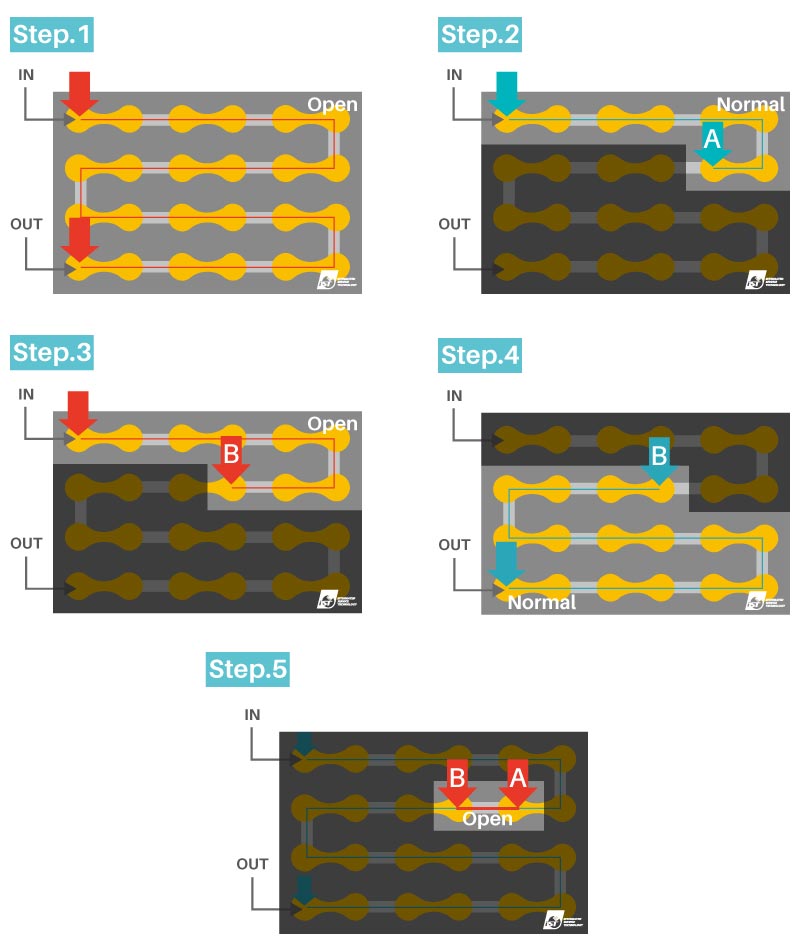

圖四:透過二分法,進行走線電性測試,一步步找到異常相對位置:圖四(1),先在IN與OUT點通電,發現Open(異常)。接著,圖四(2)在IN與A點通電,電性正常。接著,圖四(3),在IN與B點通電,顯示Open(異常)。圖四(4),在OUT與B點通電,電性正常。最後圖四(5),在B與A點通電,顯示Open(異常);藉由二分法,找到異常相對位置。

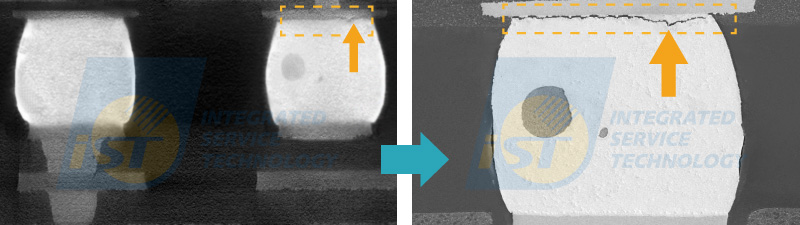

第二步驟,透過X-Ray收斂異常點,從圖五(左)中,我們可以清楚看見錫球與焊墊(Pad)連接的地方,出現異常(顯像)。第三步驟,切片進一步觀察,從圖五(右)中,則發現錫球裂開了,就此找到發生阻值異常的原因(切片)。

二、先進封裝樣品,透過EBAC,找到異常斷點

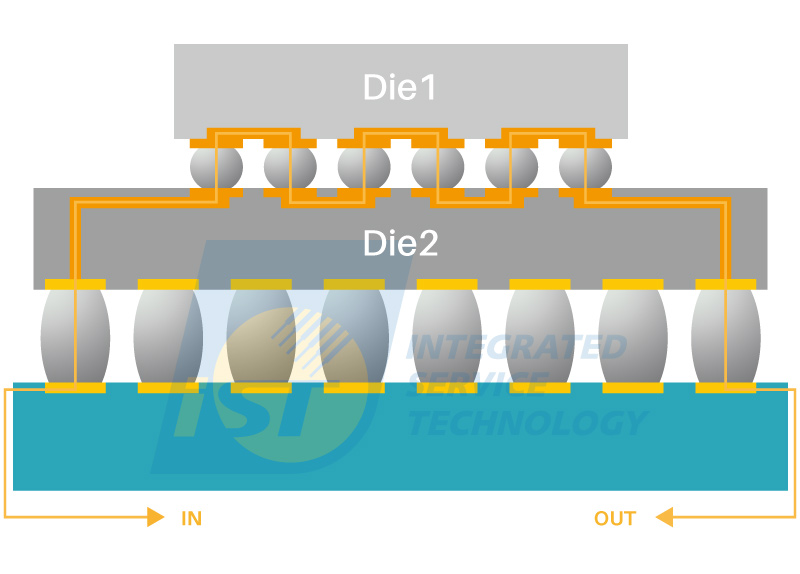

若是像2.5D或3D IC等先進封裝樣品,封裝形式屬多晶片, Daisy Chain的設計,將跳脫以往單一晶片搭配一個測試板,而是多晶片搭配在一個測試板的形式(圖六),那麼板階可靠度試驗後出現故障後,該如何找異常點呢?

若異常型態為仍有電性(Short/Leakage),可用同一般封裝樣品故障分析形式,先使用Thermal EMMI(InSb)進行熱點分析,定位異常位置,並透過X-Ray/3D X-ray顯像,最後使用Plasma FIB物性研磨,將失效斷面切出進行分析。

若異常型態為「Open」,一樣同一般封裝形式,必須在「定位」前,先進行樣品製備。不過,這邊要特別留意,一般封裝形式Daisy Chain走線是位在IC與PCB板間(參見圖七(左)),但先進封裝形式,Daisy Chain走線路徑則介於兩顆Die之間(參見圖七(右)),因此無法使用從PCB測試板端研磨的傳統方式(走線不在PCB端),就必須從晶背端,利用乾式蝕刻方式(延伸閱讀:從晶背找先進封裝錫球異常點),讓位於Die 1與Die 2間的Daisy Chain走線裸露。

圖七(左):一般封裝形式,Daisy Chain走線位於PCB與IC間;圖七(右):先進封裝形式,Daisy Chain走線位於Die 1與Die2間,透過乾式蝕刻,使Die 1的 Daisy Chain走線裸露。

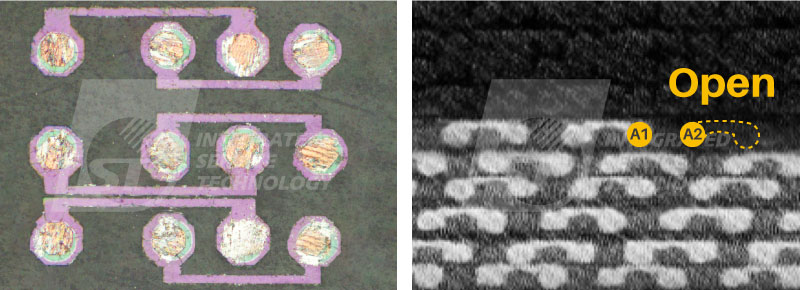

Daisy Chain裸露後(圖八(左)),我們即可進行第一步驟「定位」,因此時異常情況為Open,無法通電,就無法使用Thermal EMMI(InSb)定位Hot Spot,必須透過EBAC,將電子束導入樣品內部,電荷會累積於正常走線處,而異常處電荷無法累積,畫面就會全暗,即可判別異常位置,找到異常斷點(圖八(右))。

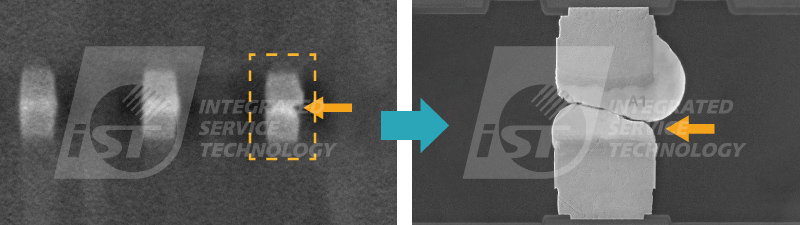

第二步驟「顯像」,安排X-ray/3D X-ray複檢,發現錫球接合異常(圖九(左))。第三步驟「切片」,安排Plasma FIB/物性研磨進行切片,找到異常現象為錫球斷裂(圖九(右))。

本篇宜特小學堂,特別提供給長久以來支持我們的客戶,若您對此實驗手法有興趣或有任何需求, 或是對相關知識想要更進一步了解細節,歡迎洽詢 +886-3-579-9909 分機 6757 楊小姐 │ Email: web_ise@istgroup.com, marketing_tw@istgroup.com