發佈日期:2021/1/21真空壓力烤箱

發佈單位:iST宜特

想確認先進封裝、IC晶片壽命與效能,

卻因Underfill製程品質不佳,Void過多導致可靠度壽命預估失準?

真空壓力烤箱

現階段,晶片採取細小間距的球閘陣列封裝(Ball grid array,簡稱BGA)、晶片尺寸封裝(Chip scale package,簡稱CSP)封裝形式的比例越來越高,因此錫球間距(Ball pitch)小於0.25公厘 (mm)以下的焊點可靠度受到關注。主要來自於,熱應力、機械應力(彎曲、扭曲)或衝擊應力作用下,細小間距的焊點可能出現斷裂失效問題。

因此,在表面黏著製程(Surface-mount technology,簡稱SMT)後,進行底部填充膠(Underfill)製程,能有效阻止焊點本身(即結構內的最薄弱點)因為應力發生應力失效,將有效增加晶片的可靠度。

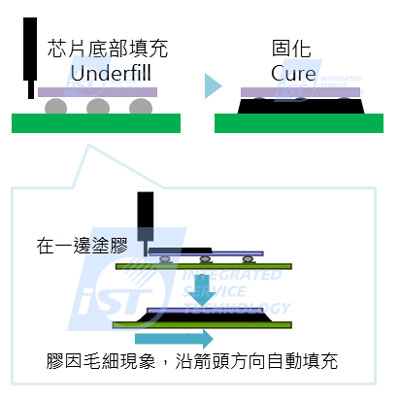

Underfill通常使用環氧樹脂(Epoxy),它的原理是利用毛細作用,將Epoxy塗抹在晶片的邊緣,使其滲透到晶片底部,完整包覆每一顆焊點,並加熱固化,藉此有效提高焊點的機械強度,進而提高晶片的使用壽命(圖一)。

Underfill製程多被運用在手持裝置,如手機或平板的電路板設計,來自於這些裝置必須通過嚴苛的衝擊試驗(Mechanical shock test)與震動試驗(Vibration test),若未進行Underfill製程,手持式裝置中晶片的焊點,將無法承受如此嚴苛測試條件。

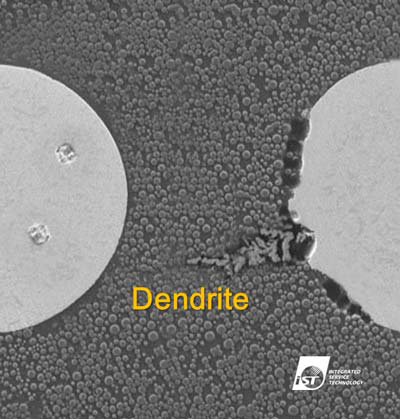

然而,在進行Underfill製程操作中,容易受到各種因素影響,或多或少會產生氣泡(Void)。這些因素包括膠管本身含有氣泡、點膠溫度及路徑、溫度固化的參數,晶片設計錫球矩陣、錫膏助焊劑成份..等,皆可能導致Underfill無法完全包覆晶片底部的錫球,大幅降低焊點保護效果。

本期宜特小學堂,將與您分享在Underfill製程中,最常產生氣泡,影響可靠度的兩種案例。

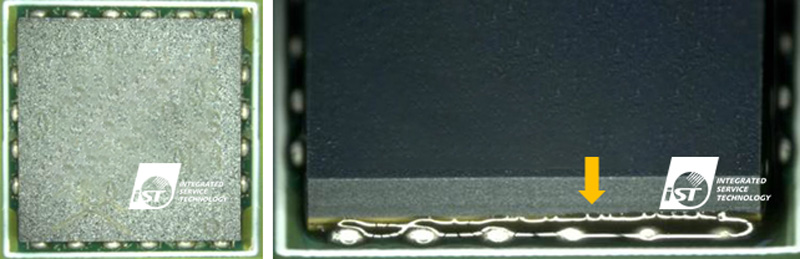

案例一: SMT製程後的焊點助焊劑(Flux)阻礙Underfill流動

案例二: Underfill無法平均滲透包覆每個焊點

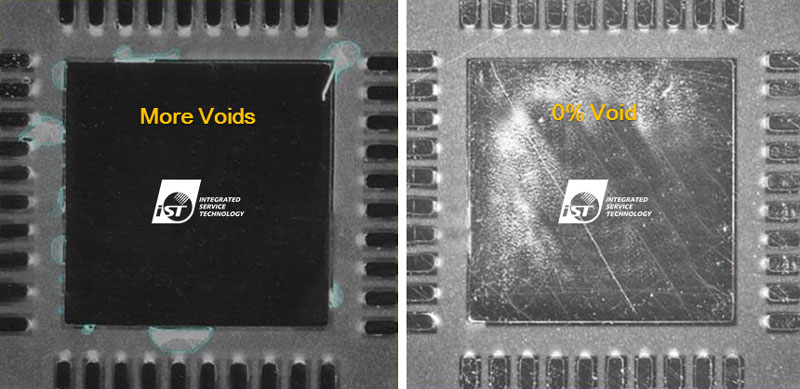

隨著先進製程將晶片極小化下,錫球間距也隨之縮小,基板(Substrate)與裸晶(Die)的間隙縮小至10-30微米(um);間隙越小,流動的速度就緩慢,進而產生空隙,因此Underfill就更難滲透,且無法平均包覆每一個焊點,因此產生氣泡。(參見圖四)

圖四: Underfill無法平均包覆每個焊點,進而產生氣泡

本文與各位長久以來支持宜特的您,分享經驗,同時,若您有小量多樣的Underfill製程需要執行,或者對相關知識想要更進一步了解細節,不要猶豫,歡迎洽+886-3-579-9909分機6429 張先生│ Email: WEB_SMT@istgroup.com。