Issued Date:2022/4/12SiP Defect

Issued By:iST

How to find suspected defects from complicated MCP/SiP structure?

How to isolate interference from other chips/dies and get correct testing results?

In response to the function diversification and micro-miniaturization of such high-tech products as multimedia and high-speed communication components, the systemic integration of components has been considered as the focus of future technology development. Currently, the system in a package (SiP) and multi-chip module (MCM) are the major trends of optimization in packaging technology.

However, when SiP or MCM failures are detected by ATE, it is often difficult to clarify which chips/dies the anomalies are coming from. This is because complicated connections through internal wiring or substrate circuit layout. The interaction of individual chips/dies makes it difficult or even impossible to have judgments.

In this session, the iST Classroom will show you a solution. With years of rich experience in semiconductor verification and analysis, iST has developed the IC repackage technology that enables harmless repackaging of the dies for testing from such SiP and MCM in an independent testing socket to keep other dies or chips away from interference while carrying out various electrical tests, in order to quickly find the causes. (Further reading: How to Transform Existing Chips into Final Test Sockets)

SiP Defect

I. Five steps for IC repackage

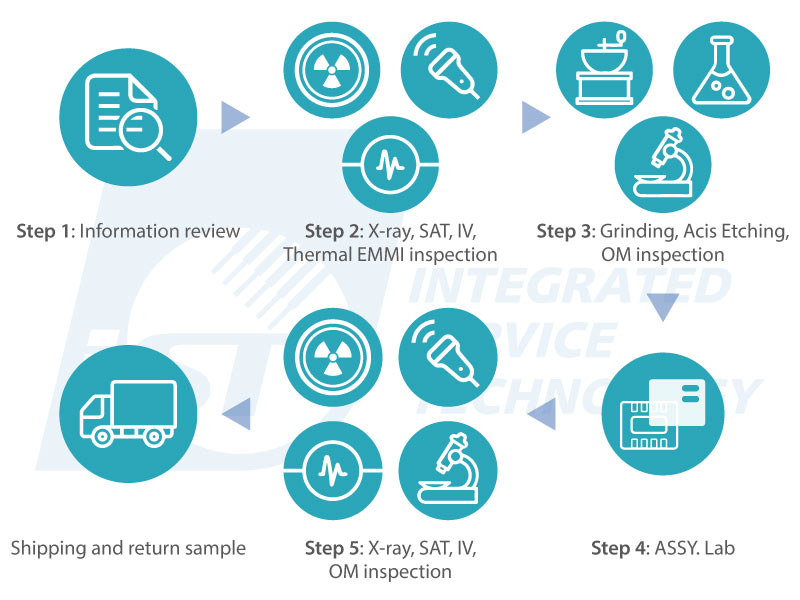

It takes five steps to achieve IC repackage at the iST Lab (Figure 1)

First, after receiving a test sample, we will run the incoming quality control (IQC) inspection and verify the related information provided by the client. The IQC includes appearance check with the 3D optical microscope (3D OM), verify the quantity of dies in the package, and the position and depth of the target (abnormal) chips. This step aims to verify if the sample condition is consistent with the client’s description.

Second, the 2D X-ray or scanning acoustic tomography (SAT) is run to verify if there is a package anomaly in the sample and confirm the position of the target (abnormal) chips required extraction. Next, the I-V curve is measured to verify the condition of the pins in the package. In addition, thermal EMMI (InSb) is applied to verify the relationships between the hot spots and target (abnormal) chips.

Third, etching and grinding are applied to extract the target (abnormal) chips and the optical microscope (OM) is used to examine if there are cracks, burnouts, or chippings on the sample.

Fourth, dies are extracted, re-bonded into the new package. Lastly, iST will run the I-V curve or notify the client to bring the repackaged IC to run the I-V curve test in-house.

Figure 1 Five steps of IC repackage at iST Lab.

II. Classic examples of IC repackage

■ Extracting target (abnormal) dies from SiP and repackage into a wBGA package.

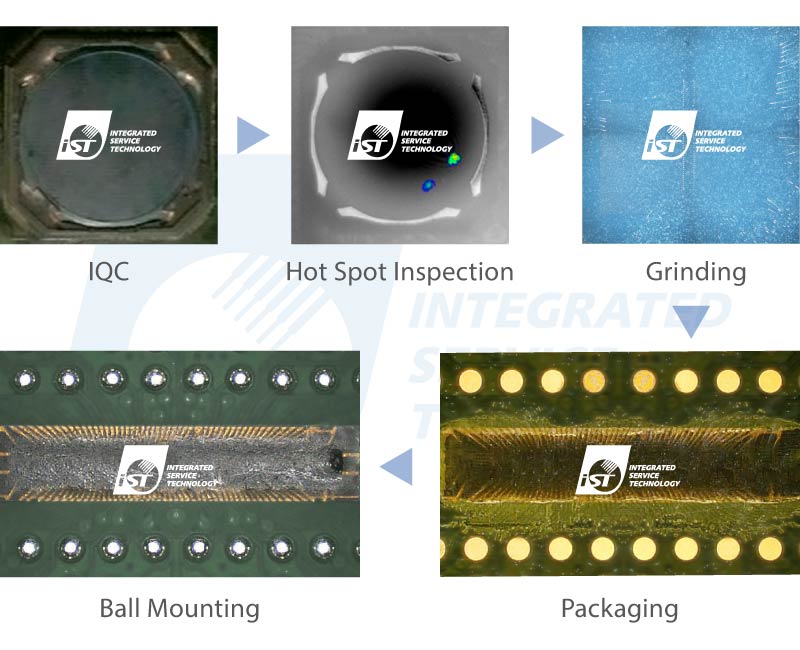

Figure 2 shows how iST extracts the target dies and repackages them into a window ball grid arrange (wBGA) package for testing. With this, clients can keep other dies away from interference while running electrical tests on the wBGA package with automatic test equipment (ATE) to confirm the position of anomalies.

Figure 2 Repackage target dies in SiP into a wBGA package to facilitate subsequent tests.

■ Extracting components from the module for ball mounting

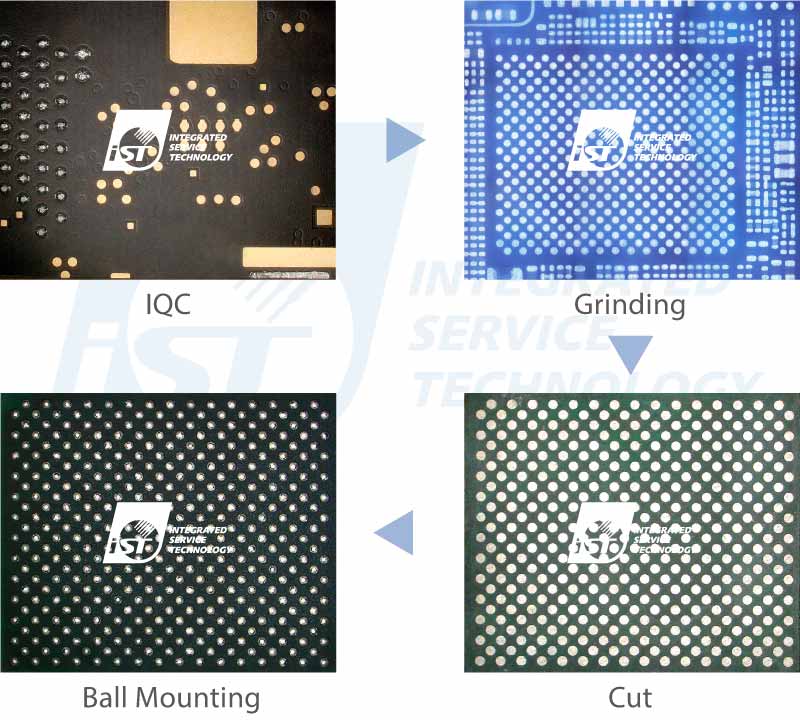

When there are many ICs or components in a module, iST Lab will extract them from the module by means of grinding or cutting for clients to verify the causes of defects with in-house tests.

The figures below show how we extract the target BGA ICs from the module. After size measuring and Ball mounting, they will become more convenient for clients to run tests.

Figure 3 After extracting and BGA packaging of the target ICs, clients can run in-house tests on them.

It’s a pleasure to share our experience with you through this article. If you are interested in learning more about the IC Repackage, please call iST at +886-3-579-9909 ext. 6755 and ask for Mr. Ou. │ Email: IST_FA_IAD@istgroup.com or marketing_tw@istgroup.com

Other services you may be interested in

SiP Defect