發佈日期:2017/11/24

發佈單位:iST宜特

針對PCB抗焊墊坑裂特性,以冷球拉力測試,驗證您的高頻高速PCB之介電材料強度

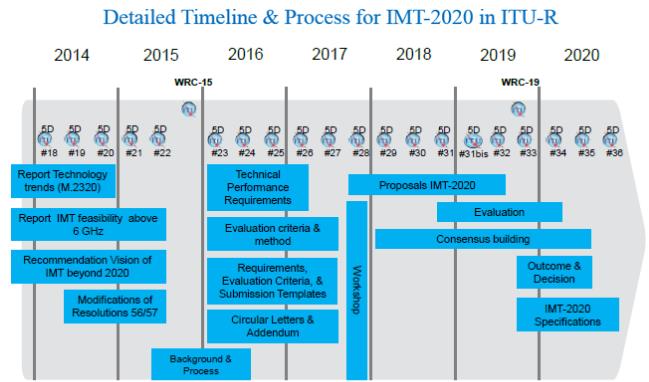

網路通訊包含有線寬頻和無線傳輸,不斷發展更為快速的傳輸速度,從3G進展到現今的4G/LTE世代,物聯網(IoT)成為未來電子產業的趨勢,國際標準組織ITU提出5G時程規劃表,預計在2020年前完成正式標準規範後開始佈建5G商用系統,訊號傳輸速度和容量的增加帶動通訊市場中的雲服務快速發展。華為數據中心研調機構預測,2015年家庭和企業等各種新應用中的82%已經使用雲端,2016年的全球電信收入中,IT雲服務收入將達到4900億美金[1],另外依國際研調機構Gartner(2016)所提出之最新資料顯示,2016年第二季全球伺服器出貨量較往年同期成長,由以中國伺服器品牌聯想、華為和浪潮出貨量百分比有顯著的二位數成長。

圖1-行動通訊4G/5G時間表 (資料來源: 國際電信聯盟ITU[2])

根據工研院2016年的統計數據顯示,銅箔基板材種類中,高速板材在2015年的年需求量成長幅度為6.6%,市場值達5.76億,隨著全球物聯網雲端應用,中國各地建設數據中心和基地台,更帶動高速板材和高耐熱板材,預估2017年的年需求量成長幅度為4.4%,市場值達6.44億。[3]因此雲端數據中心的資料儲存和數據處理的伺服器、通信設備和各終端電子設備等硬體也須支援日益提升的網路傳輸速度性能,所以在電路設計和板材選擇將需考慮高頻高速的通訊傳輸速度,絕緣材採用低介電材料(Dk: 3-4.2 @ 1GHz, Df : <= 0.005 @ 1GHz)和低粗糙度的銅導體(Low Roughness)以降低訊號傳輸的導體損失,另外電路板也須具有更高的結合強度與球徑和間距較小的BGA元件,以及較高的玻璃轉移溫度(Tg)在無鉛組裝的要求。

由於這些終端產品必須長期的使用與運作,除了必要的電氣與熱性能之外,這些基礎設備與產品也必須考慮更加嚴格的可靠度要求。並且使用較厚且大的電路板尺寸來符合基礎建設類產品的設計。另外考慮的其他因素包括:

- 以較高的填料含量,減少水分的吸收和熱膨脹係數

- 無鹵阻燃劑的熱機械可靠性和環保相容性

- 較低溫製程中,樹脂需與銅焊墊和導體有良好黏著性

- 使用矽表面處理的低介電常數玻璃纖維。

綜合上述因素,較令人擔憂的是,和過去錫鉛焊料與依常規使用未填充雙氰胺固化的介電材料相比,這些用來提高溫度和性能需求的新材料,在專門針對信息通信技術和其他處理階段的印刷電路板組裝過程中,由於IC封裝的尺寸較大、焊墊直徑較小、疊層更複雜等,將導致印刷電路板發生焊墊坑裂失效情形提高,或加快產生產品在運輸和使用壽命期間,其潛在導電性細絲物(CAF)的成長及熱機械可靠性的問題,另外,如AI人工智慧晶片以陶瓷基板作封裝為主,封裝尺寸也較大可達70mm×70mm,由於AI晶片需進行高運算處理,高I/O腳數會導致焊墊直徑較小和較細間距(Fine Pitch),因此也容易發生同樣問題。

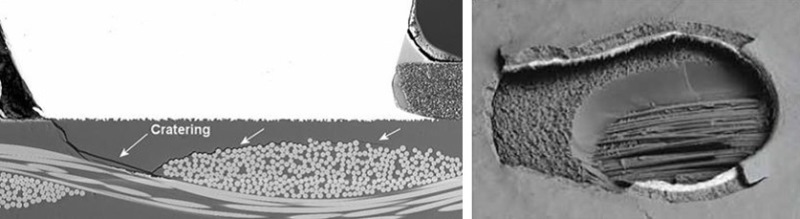

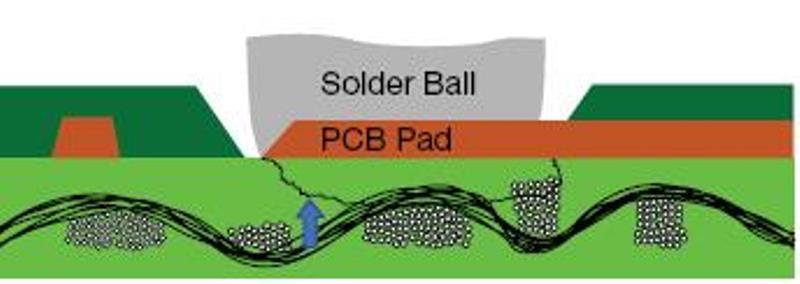

在IPC-9708中,焊墊坑裂定義是介電材料在印刷電路板中受機械應力產生的裂紋或表面黏著元件在焊墊下方的斷裂,最常見的是在BGA封裝,如圖1[5]。在印刷電路板組裝過程中,受到機械板彎或落下衝擊的應力會導致以下幾種在錫球附近的失效模式,發生這些失效模式的可能原因包含錫球焊接冶金、封裝類型、結構、組裝電路板的組件與焊墊尺寸比例、PCB材料等,在不同的應力下,通常這些失效模式有可能會同時發生。

圖1 – 焊墊坑裂在具結合力的介電材料失效裂紋往下到玻璃纖維的例子[5]

根據IPC-9708標準規定各種不同的焊墊坑裂失效模式圖例如下:

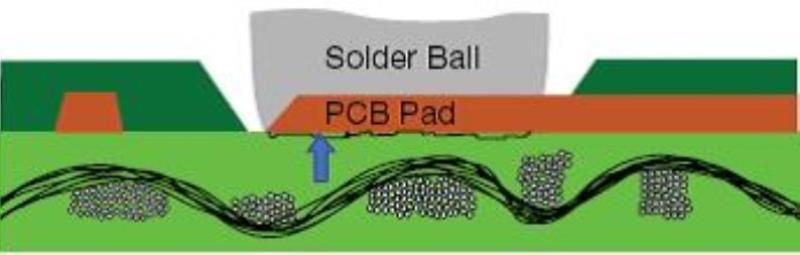

焊墊剝離(圖2):

錫球焊墊與錫球剝離 ; 剝離可能包括破裂的基礎材料。這種失效模式是一個(銅箔)接合類型失效,相對於焊墊坑裂,它是一個介電層中黏合的失效模式。

圖2-焊墊剝離

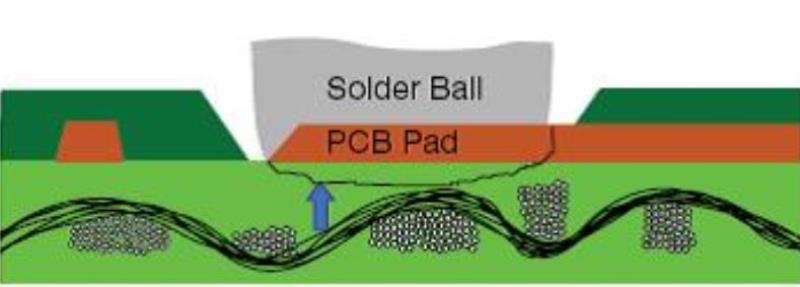

導體開裂(圖3):

印刷電路板焊墊被剝離,但仍部分連接到導體,且黏合失效。

圖3-導體開裂

玻璃纖維曝露的坑裂(圖4):

印刷電路板焊墊坑裂和底層的玻璃纖維曝露。

圖4-玻璃纖維曝露的坑裂

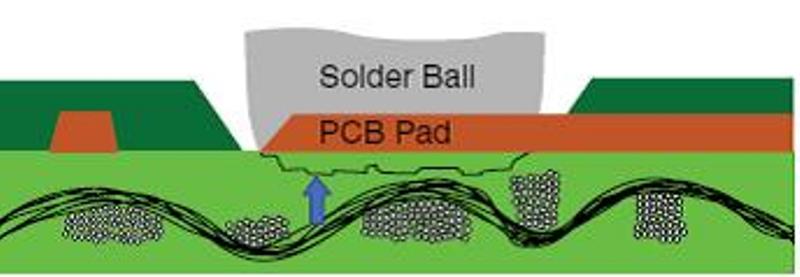

玻璃纖維沒有裸露的坑裂(圖5):

印刷電路板焊墊的坑裂,底層樹脂暴露,但沒有見到玻璃纖維,一種介電材料中樹脂的黏著失效。

圖5玻璃纖維沒有裸露的坑裂

為了減少焊墊坑裂的發生,有必要以機械應力來測試各介電材料的抗性。因此,開發了各種驗證測試方法,如機械板彎/彎曲測試、聲射檢測、落下衝擊、冷球拉力及熱針拉力等。前三種測試目的是以組裝電路板為測試載體,而最後兩種是為了以印刷電路板為測試載體。組裝電路板載體的測試通常在不同的應變和應變率下會同時產生多種失效模式,因此需花費更多時間來分離各單獨失效模式的形成原因,並從中確定裝配中最薄弱的位置。由於包含較高的動力加速度和許多變量,如焊接冶金、封裝類型、結構、組裝電路板的組件與焊墊尺寸比例及材料等,這也意味著組裝電路板級別測試並沒有時間及成本效益。而焊墊載體測試中,它更易於控制焊墊下方介電層的失效模式,並定義焊墊、樹脂和玻璃纖維之間的黏合力。在此研究中所提及的這兩種焊墊級別的測試,因為冷球拉力試驗過程中沒有本身引起額外的變異熱量介入試驗,所以試驗過程中產生的變異數比熱針拉力試驗更容易控制。

這項研究中,介電材料的3種基本類型包括有:

- 高玻璃轉移溫度(無酚醛填料)FR4

- 高玻璃轉移溫度(無鹵)FR4

- 高速材料類。

這3類材料在冷球拉力(CBP)的試驗所造成焊墊坑裂的效果會有較佳的敏感性。

實驗的設置和步驟

測試板

表1列出了本研究中所使用來自不同材料製造商的介電材料的機械特性與特點,這些材料都是專門為高性能伺服器、網路和通信應用而設計。該材料是由數個製造商提供,並且全部都符合無鉛工藝規範要求。該疊層包括6層的介電材料,所有的電路板層疊在相同的印刷電路板上。最終的測試板尺寸為60mm(長)×60mm(寬)×2.2mm(厚)。並用化錫做表面處理。

銅箔

基板材料類型 樹脂含量

(%)1OZ的剝離強度

(lb/in)彎曲強度

(MPa)製造商 A 高玻璃轉移溫度(無鹵)FR4 53 4.5 460~500 M1 B 高速材料 53 4.0 420~450 M1 C 高玻璃轉移溫度(無鹵)FR4 53 5.1~6.8 >400 M3 D 高速材料 53 5.5 400 M4 E 高玻璃轉移溫度無填料的酚醛FR4 53 8~11 >380 M2 F 高速材料 53 5~7 >350 M2 表1 -不同介電材料的特性與特點 (* IPC4101C規格表與製造商的數據)

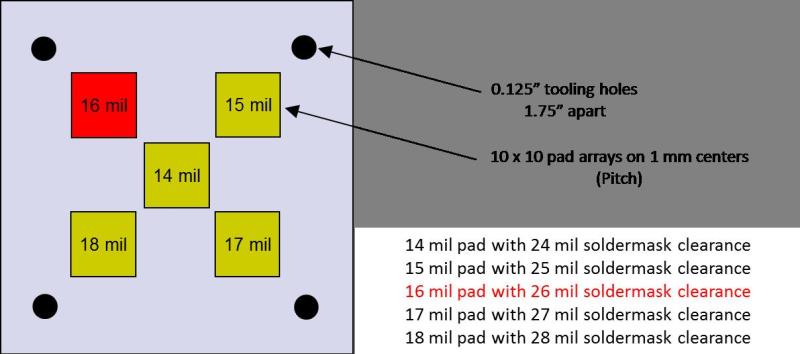

每個測試板有5個測試區域(10mm×10mm),每個區域具有不同焊墊尺寸,範圍從14mil至18mil以1mil遞增。焊墊在設計與實際的直徑有差異,因此必須先測量並選取實際直徑為16mil的焊墊進行試驗來減少變異。其中所有的焊墊皆以非阻焊層限定(NSMD)設計,並且所有焊墊與阻焊層之間保持5mil的間隙(如圖6),使焊墊與焊料球有最佳的結合空間。

圖6-測試板的設計

實驗流程

圖7的示意圖說明整個實驗流程,必須用光學顯微鏡(OM)進行測定所有的焊墊直徑,並選取直徑在16mil ±1%範圍的焊墊來做研究試驗。

圖7-實驗流程

植球

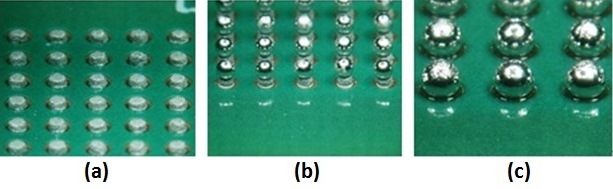

首先將測試板放置到一個固定治具上,利用網板將SAC錫膏印刷至測試板的焊墊上,再使用20mil直徑的SAC錫球,然後利用落球網板使錫球落在錫膏上。錫球附著於均勻塗佈的錫膏後,移除落球網板(參見圖8-(a) & 9-(b))。再經過迴焊爐烘烤並在迴焊過程中加入氮氣防止樣品被氧化 (參見圖8-(c))。

圖8 – (a)錫膏塗佈 (b)落球位置 (c)經迴焊後,錫球與測試板的結合

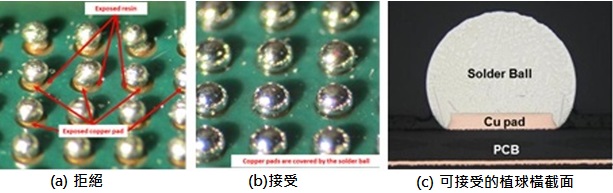

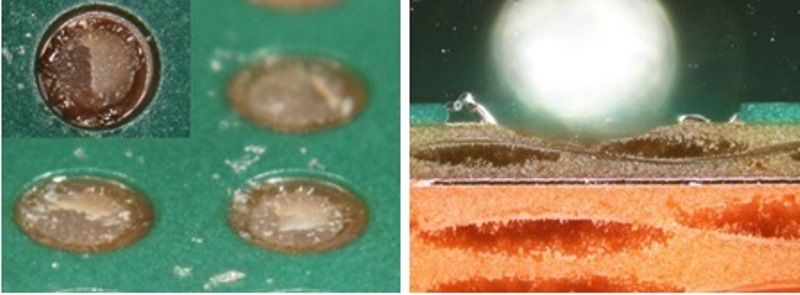

圖9表示植球的合格參考標準。任何一個經迴焊之後的錫球下方如有露銅,結合強度會受影響,故將排除該球進行冷球拉力試驗。只有焊墊被焊料完全覆蓋與結合才認為是可以接受的,如圖9-(b)和9-(c)所示。

圖9 – 植球的參考標準

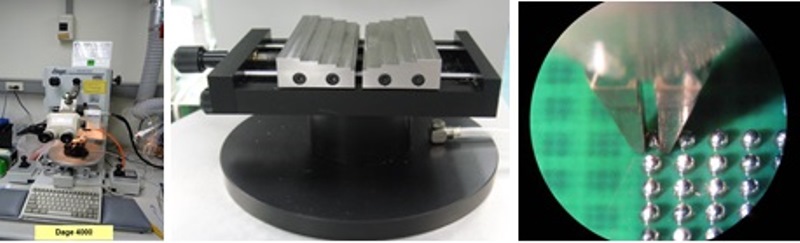

冷球拉力試驗的設置

圖10的冷球拉力設備裝置可使用同一種夾具操作測試,並用於一定範圍內各種不同尺寸的錫球。

圖10 -(a)冷球拉力測試設備 (b)測試板固定台(c)拉球夾具

收集數據

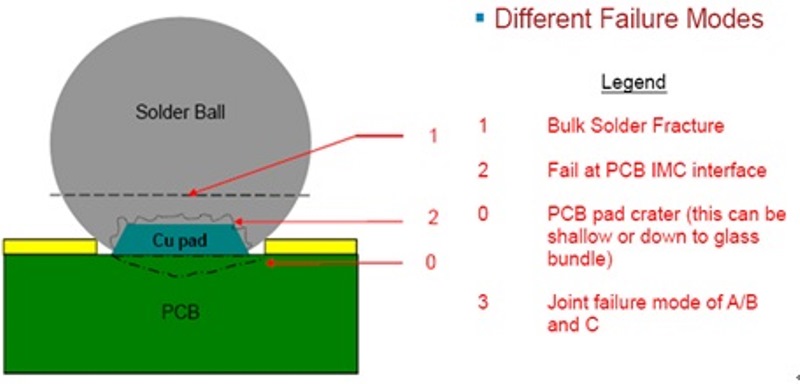

在焊墊直徑16mil的陣列中選取50個點做拉力測試,每種材料有5片測試板,每片測試板選擇50個點,所以共有250點做拉力測試數據,測試後再以統計軟體來做分析統計。測試後產生的失效模式會根據材料 、製程流程和幾何設計而有所不同。這些失效模式包括:

- 錫球斷裂

- 金屬合金IMC層的斷裂

- 印刷電路板的焊墊坑裂,或是以上失效模式的綜合(見圖11)。

本研究的重點方面在於印刷電路板的焊墊坑裂失效模式,失效種類可以分為4類,包括:

- 焊墊剝離

- 導體開裂

- 玻璃纖維曝露的坑裂

- 玻璃纖維沒有裸露的坑裂 ,(參見圖2~圖5)。

裂紋本身會依循阻力最小的路徑延伸來減輕應力,一開始可能沿著焊墊邊緣穿過整個樹脂向下蔓延,或集結在焊墊下方的樹脂和玻璃纖維之間,或斷裂至焊墊(導體)下方的介電層。這個坑裂失效可能不會馬上導致電路斷路,但之後可能在運輸和持續的使用下導致裂紋擴展引起電氣故障。

結果與討論

冷球拉力的典型失效模式

圖11 – 冷球拉力測試過程中的典型失效模式

介電材料的設計有許多變數,如:樹脂成分、固化劑、玻璃樹脂含量、填料的含量等,找出哪個才是提高抗斷裂性以減輕失效的最大因子是相當不容易的。從斷裂力學的觀點來看,在基質中不同成分之間的黏合力是難以透過這種測試方法來量化。原因是當裂紋發生時,樹脂材料本身可以吸收大部分斷裂能量,裂縫深度分佈的失效模式是隨機的。因此,單靠一種測試的基礎上,我們只能斷定改善樹脂本身的斷裂韌性是一個提升材料性能的方向。遺憾的是,對這些材料並沒有一套標準的方法或規定可用於測試抗斷裂韌性。因此只能使用一般的機械性質以尋求關聯性,如:彎曲模數、彎曲強度及剝離強度。

一、Halogen-free介電材料結果與討論

冷球拉力(CBP)試驗的目的是藉由從焊墊上的焊球垂直往上拉動,來觀察焊墊(Cu Foil)與其下面介電材料之間斷裂的強度。雖然這項測試不足以確認裂紋的起始點與擴展軌跡,但可以量化整個斷裂過程的總能量。

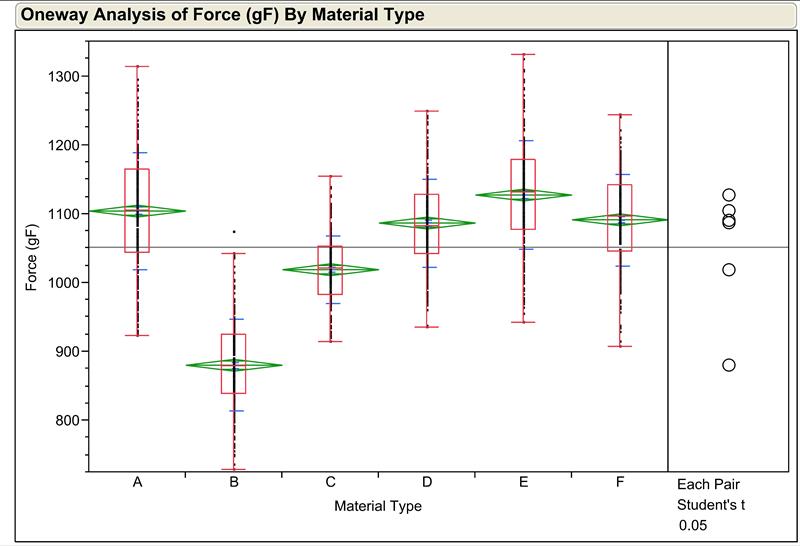

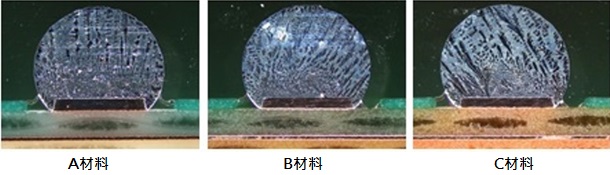

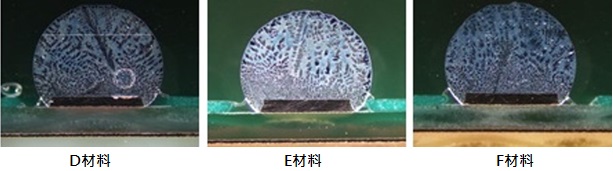

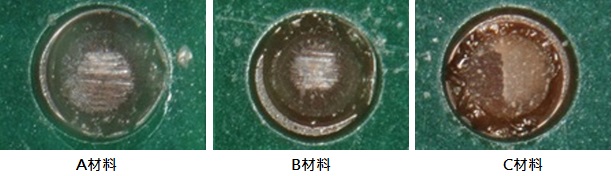

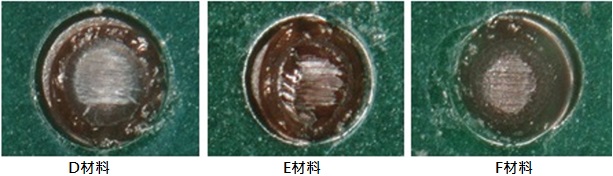

圖12和表2顯示6種材料在冷球拉力試驗中的斷裂強度。我們可以觀察到這六種材料在結果上有些微的不同,其中B類材料可觀察到較低的斷裂強度(約880克)。而這六種材料的標準差都在可接受範圍內,使得其所擁有的斷裂強度平均值是可以作為比較的。並且從這6種材料各拿一片去做橫截面,確定其中沒有焊點缺陷的存在,如:空焊、冷焊、空洞等,因為這些因素會影響整個試驗的結果(見圖11)。高玻璃轉移溫度(無酚醛填料)FR4(材料E)的拉力強度優於高玻璃轉移溫度(無鹵)FR4(材料A、C)與高速材料類(材料B、D、F),這說明了較少的樹脂填料含量可能增強附著力或降低樹脂的脆性。表1還顯示出材料E(製造商M2)有最高的剝離強度(對於銅有很好的附著力)。由圖12可以觀察到E材料的失效為IPC-9708規範中”玻璃纖維曝露的坑裂”失效模式(見圖4)。這種失效類型可能是較為理想的失效模式,顯現其對於焊墊坑裂有較高的抗性。

相較之下,在這項研究中表現最差的B材料(高速材料)也有類似的失效模式,但玻璃纖維斷裂的區域比樹脂大。人們一般認為較高的填料含量樹脂是降低電介質的介質常數和熱膨脹係數的理想設計,但其副作用是增加脆性和彈性係數或減少樹脂對玻璃纖維的附著力。表1說明材料B(製造商M1)因其更脆的材料、銅箔特性與低黏附性而顯示出較低的剝離強度。另一方面,D與F這兩種高速材料為不同製造商提供(M2與M4)雖然與B材料有相同的樹脂含量(皆為53%),但冷球拉力與剝離強度皆比B材料高。所以在填裝過程中,樹脂的化學特性會影響其密合度。(注:填料的質量比例是未知的,但可以再進一步研究討論。)

A和C材料為高Tg無鹵FR4s設計但來自不同製造商(M1和M3),其冷球拉力測試強度相似,但失效模式卻不同(圖12)。在A材料的失效模式是類似於上面提到的那些帶有部分外露加上樹脂破裂的玻璃纖維,而C材料中的失效位置似乎在樹脂層中,是屬於”玻璃纖維沒有裸露的坑裂”的失效類型(圖5)。之後使用橫截面觀察側面並進一步分析(圖13) 可以得出結論:失效模式仍然是在圖5的類型並表示出不同的玻璃纖維結構。阻燃劑從溴化類型轉換到無鹵類型通常會降低樹脂對銅和玻璃纖維的黏著性。為了提高性能,建議修改樹脂的化學成分或施加偶合劑到玻璃纖維(浸漬之前)來增加黏合力。

圖12- 6種介電材料的冷球拉力試驗強度

銅箔

基板製造商 材料類型 標準差 平均值

(克)A M1 高玻璃轉移溫度(無鹵)FR4 84.76 1104.2 B M1 高速材料 66.7 880.5 C M3 高玻璃轉移溫度(無鹵)FR4 48.6 1019.2 D M4 高速材料 64.2 1086.9 E M2 高玻璃轉移溫度無填料的酚醛FR4 78.6 1127.5 F M2 高速材料 66.4 1091.6 表2 – 冷球拉力測試的數據 (樣品數:250顆/材料)

圖13- 6種材料在冷球拉力試驗前的橫截面

圖14- 冷球拉力試驗後,光學顯微鏡下的失效模式

圖15-冷球拉力試驗後,C材料的橫截面側視圖

二、超低損耗介電材料 (Dk: 3-4.2 @ 1GHz, Df : <= 0.005 @ 1GHz)的應用與討論

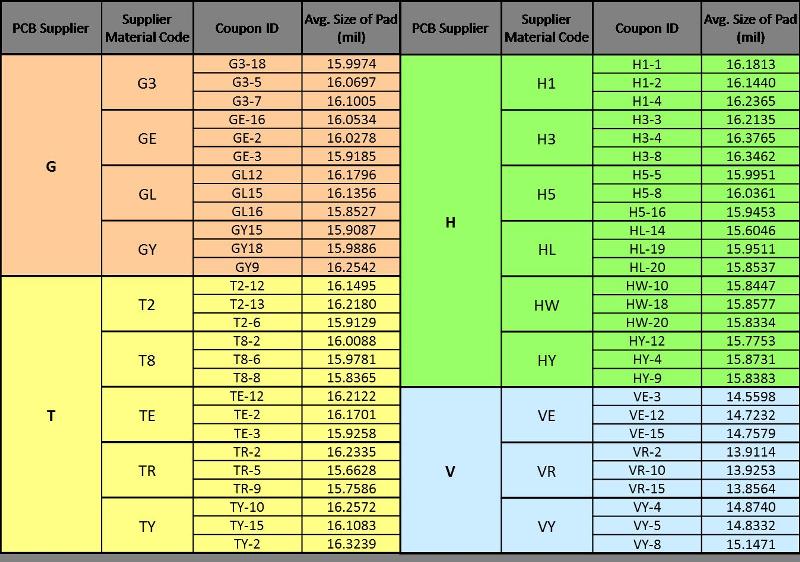

參考自作者於2017年2月在IPC-APEX發表的Cold Ball Pull Test Efficiency for the PCB Pad Cratering Validation with the Ultra Low Loss Dielectric Material論文[6],此篇論文提到即使印刷電路板使用相同的介電材料和電路板的疊構,並依照同一份電路板設計圖和板材所製作的電路板,其成品仍會因為不同的電路板廠製程設定影響而會有所不同,表3為銅焊墊的實際量測值(從16到18mils),測試板材是由4間板廠所提供的印刷電路板,經量測後選擇銅焊墊大小的實際值接近16mils進行冷球拉力測試。

表 3– 選擇PCB焊墊大小進行冷球拉力試驗[6]

在先前部分介紹到IPC-9708標準規定各種不同的焊墊坑裂失效模式可作為介電材料強度判斷的依據。以下列出不同材料在各別板廠的表現評比。

- G 廠:G3>GL>GE>GY

- H 廠:H1>HW>H3>H5>HL>HY

- V 廠:VR>VY>VE

- T 廠:TY>TR>T8>TE>T2

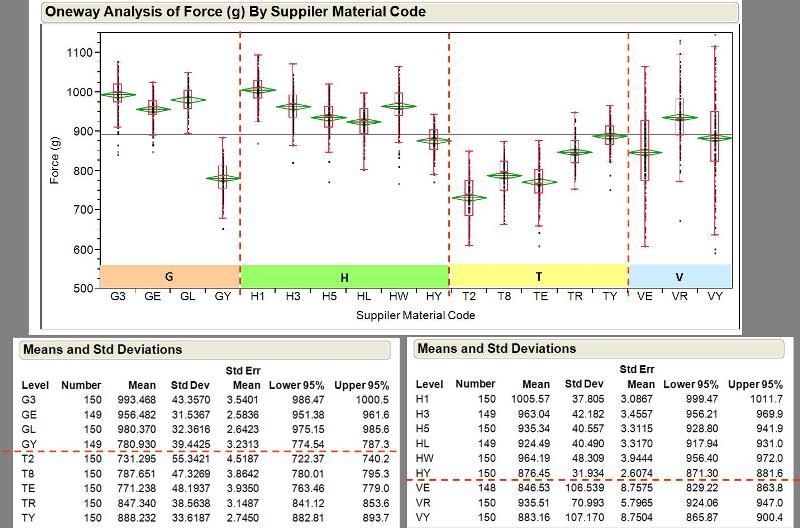

由圖16的箱型圖顯示每種介電材料的平均數和標準差,從數據可以看到雖然是相同的材料,但在不同板廠製作下有不同的表現結果;反之,不同的材料在同一版廠製作下的結果。例如,材料TY的強度在板廠T的製程和板廠G的製程相比之下,在板廠T的製程下表現顯著優秀。另外,在相同的G板廠製程下,材料G3的強度表現比材料GY優秀。板廠製程設定的不確定因素和銅焊墊的大小皆會影響電路板的表現性,因此藉由材料強度的評比結果可瞭解介電材料在每間板廠的強度表現。電路板廠可藉由此冷球拉力試驗評估哪種介電材料在廠內製程下有最好的表現,以降低因焊墊坑裂所導致的退貨率;但是也因為板廠製程設定的變數影響,無法就結果判定不同介電材料表現性的強弱。

圖 16-冷球拉力試驗後,介電材料強度的表現性[6]

結果

參考自IPC-9708的冷球拉力測試是用來描述不同介電材料的焊墊坑裂性能。謹慎執行此測試實驗且沒有出現異常結果時,即可證明這是可再現的測試方法,意味著在實務上這是一個良好的測試方法。雖然此研究無法明確的指出介電材料在通過何種冷球拉力強度後是有能力承受在產品實際的運送及使用中的電路板焊墊坑裂,但能夠1.提供在樹脂系統的選擇和設計的指標,這些要素將影響焊墊坑裂相關的敏感性,從而使終端用戶能夠選擇最佳的材料。2. 讓電路板廠可藉由冷球拉力試驗評估數種材料在廠內製程設定下,選擇有最佳表現性的材料。還有其他的測試方法與此研究相關,如:衝擊試驗、球形彎曲測試、動態力學分析(DMA)等在持續進行。

參考文獻:

[1] “華為數據中心SDN,構建雲時代敏捷網路”, 2016, http://www.c114.net/news/126/a957070.html

[2] “Futuristic mobile technologies foresee “IMT for 2020 and beyond”” http://www.itu.int/en/ITU-R/study-groups/rsg5/rwp5d/imt-2020/Pages/default.aspx

[3] 張致吉, “從高質化PCB的應用市場看材料產業的佈局”, 工業材料No.358, Oct. 2016, pp. 54-59

[4] 金進興, “材料設計與高頻高速電路”, 工業材料No.358, Oct. 2016, pp. 136-144

[5] IPC-9708, Test Methods for Characterization of Printed Board Assembly PadCratering,2010.

[6] Jeffrey ChangBing Lee, Gary Long, Masahiro Tsuriya, “ Cold Ball Pull Test Efficiency for the PCB Pad Cratering Validation with the Ultra Low Loss Dielectric Material”, IPC/APEX, 2017

[7] Mukadam, M., Long, G., Butler, P., Vasudevan, V., “Impact of Cracking Beneath Solder Pads in Printed Circuit Boards on the Reliability of Ball Grid Array Packages”, Proc SMTAI, 2005, pp. 324-329.

[8] Roggeman, B., Borgesen, P., Li, J., Godbole, G., Tumne, P.,Srihari, K.., Levo, T., Pitarresi, J., “Assessment of PCB Pad Cratering Resistance by Joint Level Testing”, Proc 58th Electronics Components and Technology Conference, May 2008, pp. 884-892K.

[9] Ahmad, M., David, S., Burlingame, J., “Methodology To Characterize Pad Cratering Under BGA Pads In Printed Circuit Boards”, Proc. SMTA PanPacific Microelectronics Symposium, Kauai, HI, 2008.

[8] Ahmad, M., Burlingame, J., Guirguis, C., “Comprehensive Methodology To Characterize And Mitigate BGA Pad Cratering In Printed Circuit Boards”, SMTA Journal, Vol. 22, No. 1, 2009, pp. 21-28.

[10] Ahmad, M., Burlingame, J., Guirguis, C., “Validated Test Method to Characterize and Quantify Pad Cratering Under BGA Pads on Printed Circuit Boards”, Proc APEX Expo, Las Vegas, NV, March 2009.

[11] Roggeman, B.,, Venkatesh Raghavan, Peter Borgesen, “Joint Level Test Methods for Solder Pad Cratering Investigations”, Accepted for publication Journal of Electronics Packaging, March 2011.

[12] Godbole, G., Roggeman, B., Borgesen, P., and Srihari, K.,“On the Nature of Pad Cratering”, Proc 59th Electronics Components and Technology Conference, May 2009, pp. 100-108.

[13] McMahon, J., Gray, B., “Mechanical Failures in Pb-Free Processing: Evaluating the Effect of Pad Crater Defects on Process Strain Limits for BGA Devices”, Proc.SMTA PanPacific Microelectronics Symposium, 2010.

[14] Gray, B., McMahon, J., “Mechanical Failures in Pb-Free Processing: Selected Mitigation Techniques for Pad Crater Defects”, Proc SMTAI, 2010, pp. 530-534.

[15] Raghavan, V., Roggeman, B., Meilunas, M., Borgesen, P., “Effects of Pre-Stressing on Solder Joint Failure by Pad Cratering”, Proc 60th Electronics Components and Technology Conference, May 2010, pp. 456-463.

[16] IPC/JEDEC-9702, “Monotonic Bend Characterization of Board Level Interconnects”

[17] Brian Roggeman and David Rae,S,”Reliability Impact of Partial Pad Crater”,SMTA International Conference Proceedings,2012.

[18] Anurag Bansal, Cherif Guirguis and Kuo-Chuan Liu, “Investigation of Pad Cratering in Large Flip-Chip BGA using Acoustic Emission”,IPC/APEX 2012.

[19] M. Ahmad et al, “Validated Test Method To Characterize And Quantify Pad Cratering Under BGA Pads On Printed Circuit Boards”, IPC/APEX 2009 Conference, Las Vegas, NV, April, (2009)區塊

本文作者:

陳承志/李長斌

宜特科技- 國際工程發展處