发布日期:2018/3/27

发布单位:iST宜特

IC出现短路,进行开盖(De-cap)后,短路现象却消失了,怀疑是封装体有缺陷,如何找Defect?

身为IC设计工程师的你,应该常遇到类似的问题。IC出现漏电、短路等异常电性问题,以为是自己的电路设计有问题,因此,来宜特进行IC开盖(De-cap),準備做InGaAs、EMMI、OBIRCH等电性量测前,却发现,IC开盖后,所有的电性异常问题都消失了,IC恢复正常了。此时心情一则以喜、一则以忧,确定至少不是自己的设计有问题,但会是哪儿有问题呢?

这时候,问题就指向了「封装体」。我们怀疑,有可能是封装制程本身的缺陷。

一般而言,要找IC缺陷,通常需要用「破坏封装体的方式」,包括IC开盖、去黑胶等方式先进行样品前制作业,但如果有可能是「封装体」的问题,就不能使用破坏性的检测方式。

本月小学堂,将带来如何以不破坏样品本身的方式,来找IC的Defect。

第一步骤:定位

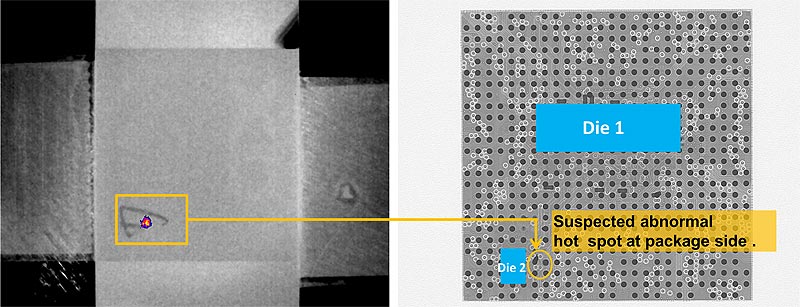

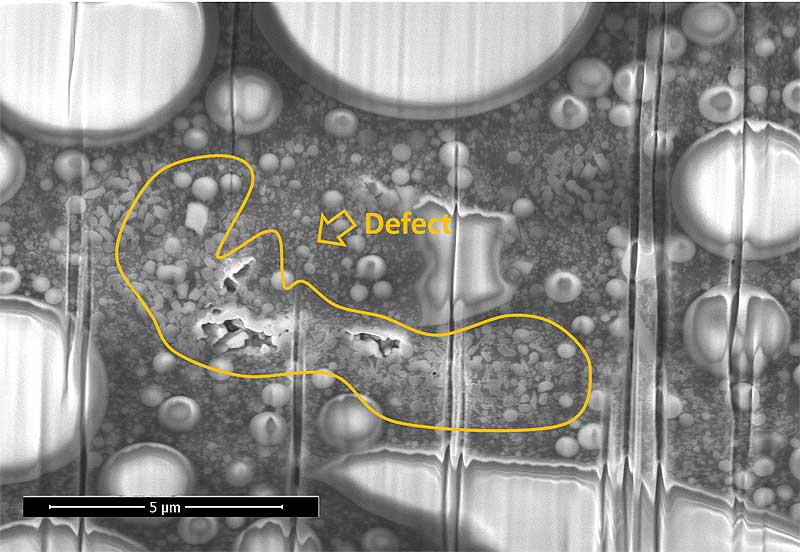

在IC通电的状态,且不破坏样品的原貌下,利用Thermal EMMI故障点热辐射传导的相位差,侦测 IC封装的故障点深度(Z轴方向),快速定位故障点XYZ坐标位置,并找到该异常点不是在Die 2本身,而是在封装体的打线区(见图一)。

第二步骤:显像←→定位 来回验证,缩小异常定位点,厘清相关异常点位置

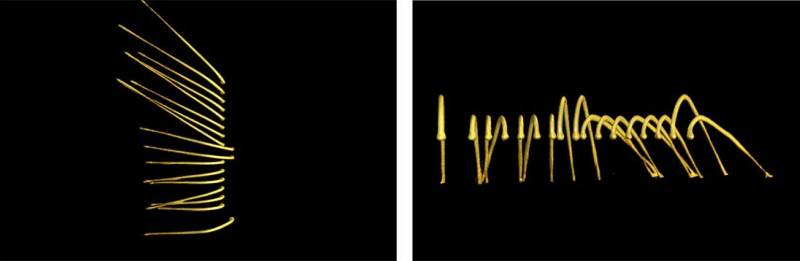

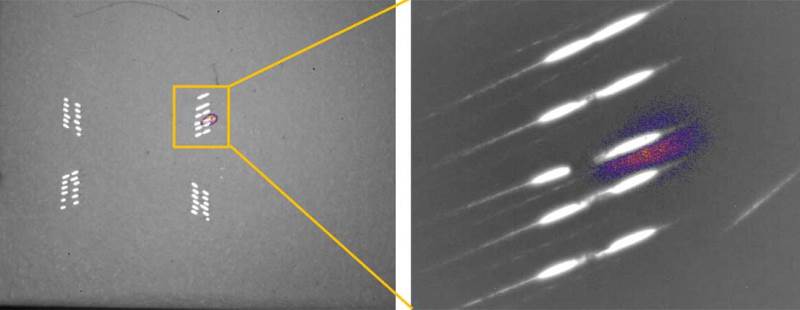

利用3D X-ray,将失效位置影像在非破坏的状态下,呈现出3D立体图,检视相关所定位之处是否有相关异常点(见图二);若无明显异常,需再将样品作适当的处理后,执行「再定位分析」,让相关异常点更明显呈现,以利于后续相关分析(见图三)。

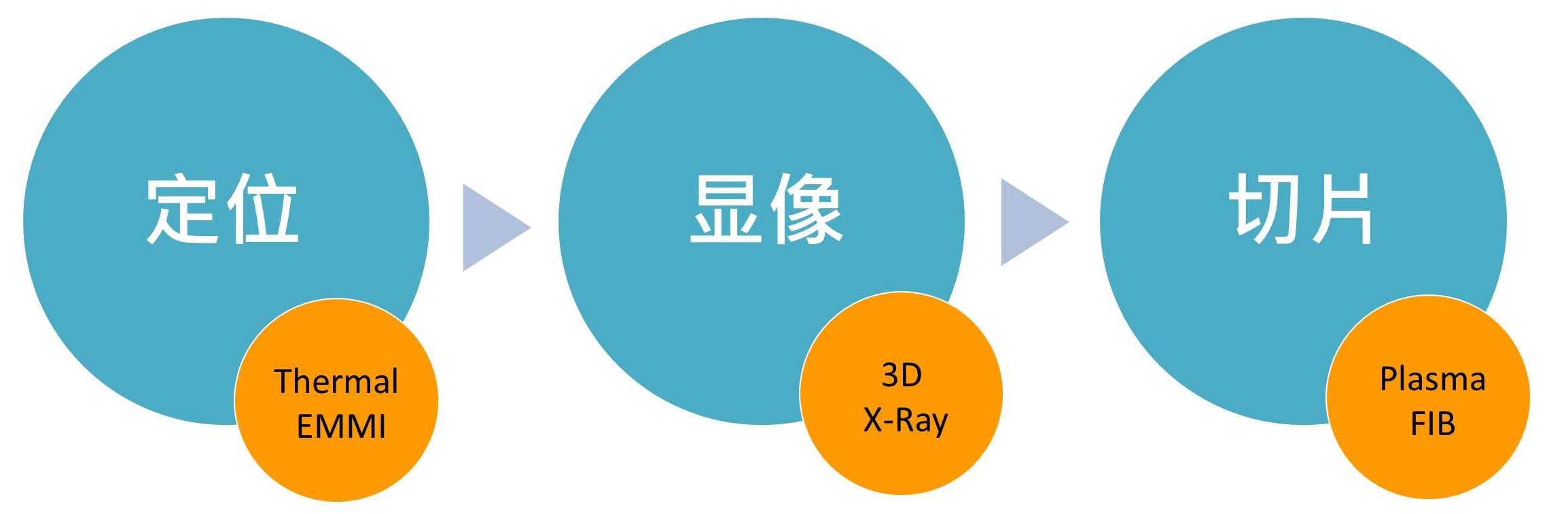

第三步骤:切片

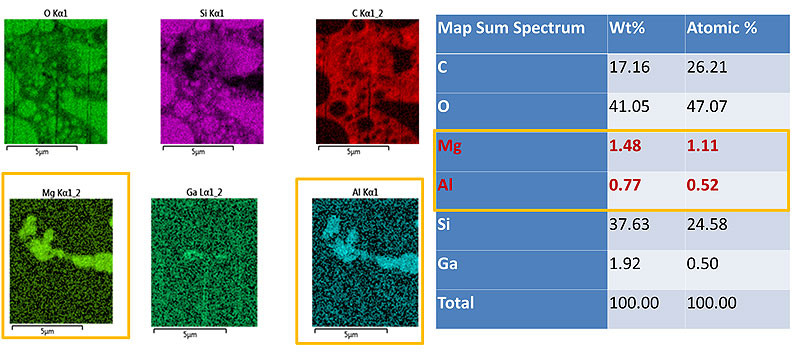

IC组件在封装BOM的搭配上应力较弱,必须选择低应力工具。但若使用传统人工研磨,应力会产生严重破坏,因此选择,利用低应力Plasma FIB将失效断面切出并分析真因,找到封装体内,原来含有不该出现的金属物质-镁(Mg)与铝(Al),因而导致封装体有异常漏电缺陷(见图四)。此时也厘清了,在第二步骤时,为什么利用3D X-ray观测不到异常点(3D X-ray会穿透镁铝这种较为松散的金属,而无法显像)。

图四:FIB X-S 显示,封装体缺陷含有镁(Mg)与铝(Al)的物质,此为造成 IC 电性异常的原因

本文与各位长久以来支持宜特的您,分享经验,若您任何IC异常状况不知如何分析,或是对相关知识想要更进一步了解细节,欢迎洽中国免费咨询电话:400-928-9287│ Email: marketing_chn@istgroup.com